## 3 V supervisor with battery switchover

### Features

- RST or  $\overline{\text{RST}}$  outputs

- NVRAM supervisor for external LPSRAM

- Chip enable gating (STM795 only) for external LPSRAM (7 ns max prop delay)

- Manual (push-button) reset input

- 200 ms (typ)  $t_{\text{rec}}$

- Watchdog timer - 1.6 s (typ)

- Automatic battery switchover

- Low battery supply current - 0.4  $\mu\text{A}$  (typ)

- Power-fail comparator (PFI/ $\overline{\text{PFO}}$ )

- Low supply current - 40  $\mu\text{A}$  (typ)

- Guaranteed  $\overline{\text{RST}}$  (RST) assertion down to  $V_{\text{CC}} = 1.0$  V

- Operating temperature:

–40 °C to 85 °C (industrial grade)

- RoHS compliance

- Lead-free components are compliant with the RoHS directive

1. Contact local ST sales office for availability.

**Table 1. Device summary**

|             | Watchdog Input | Active- low RST <sup>(1)</sup> | Active- high RST <sup>(1)</sup> | Manual reset input | Battery switchover | Power-fail comparator | Chip enable gating |

|-------------|----------------|--------------------------------|---------------------------------|--------------------|--------------------|-----------------------|--------------------|

| STM690T/S/R | ✓              | ✓                              |                                 |                    | ✓                  | ✓                     |                    |

| STM704T/S/R |                | ✓                              |                                 | ✓                  | ✓                  | ✓                     |                    |

| STM795T/S/R |                | ✓ <sup>(2)</sup>               |                                 |                    | ✓                  |                       | ✓                  |

| STM802T/S/R | ✓              | ✓                              |                                 |                    | ✓                  | ✓                     |                    |

| STM804T/S/R | ✓              |                                | ✓ <sup>(2)</sup>                |                    | ✓                  | ✓                     |                    |

| STM805T/S/R | ✓              |                                | ✓ <sup>(2)</sup>                |                    | ✓                  | ✓                     |                    |

| STM806T/S/R |                | ✓                              |                                 | ✓                  | ✓                  | ✓                     |                    |

1. All  $\overline{\text{RST}}$  outputs push-pull (unless otherwise noted).

2. Open drain output.

## Contents

|          |                                                   |           |

|----------|---------------------------------------------------|-----------|

| <b>1</b> | <b>Description</b>                                | <b>6</b>  |

| 1.1      | Pin descriptions                                  | 9         |

| 1.1.1    | $\overline{MR}$ (manual reset)                    | 9         |

| 1.1.2    | WDI (watchdog input)                              | 9         |

| 1.1.3    | $\overline{RST}$ (active-low reset)               | 9         |

| 1.1.4    | RST (active-high reset - open drain)              | 9         |

| 1.1.5    | PFI (power-fail input)                            | 9         |

| 1.1.6    | $\overline{PFO}$ (power-fail output)              | 9         |

| 1.1.7    | $V_{OUT}$ (supply output voltage)                 | 9         |

| 1.1.8    | $\overline{V_{CCSW}}$ ( $V_{CC}$ switch output)   | 9         |

| 1.1.9    | $\overline{E}$ (chip enable input)                | 10        |

| 1.1.10   | $\overline{E}_{CON}$ (conditional chip enable)    | 10        |

| 1.1.11   | $V_{BAT}$ (backup battery input)                  | 10        |

| <b>2</b> | <b>Operation</b>                                  | <b>14</b> |

| 2.1      | Reset output                                      | 14        |

| 2.2      | Push-button reset input (STM704/806)              | 14        |

| 2.3      | Watchdog input (NOT available on STM704/795/806)  | 14        |

| 2.4      | Backup battery switchover                         | 15        |

| 2.5      | Chip enable gating (STM795 only)                  | 16        |

| 2.6      | Chip enable input (STM795 only)                   | 16        |

| 2.7      | Chip enable output (STM795 only)                  | 16        |

| 2.8      | Power-fail input/output (NOT available on STM795) | 17        |

| 2.9      | Applications information                          | 17        |

| 2.10     | Using a SuperCap™ as a backup power source        | 19        |

| 2.11     | Negative-going $V_{CC}$ transients                | 19        |

| <b>3</b> | <b>Typical operating characteristics</b>          | <b>20</b> |

| <b>4</b> | <b>Maximum ratings</b>                            | <b>30</b> |

| <b>5</b> | <b>DC and AC parameters</b>                       | <b>31</b> |

|   |                                |    |

|---|--------------------------------|----|

| 6 | <b>Package mechanical data</b> | 36 |

| 7 | <b>Part numbering</b>          | 39 |

| 8 | <b>Revision history</b>        | 41 |

## List of tables

|           |                                                                                               |    |

|-----------|-----------------------------------------------------------------------------------------------|----|

| Table 1.  | Device summary . . . . .                                                                      | 1  |

| Table 2.  | Signal names . . . . .                                                                        | 7  |

| Table 3.  | Pin description . . . . .                                                                     | 10 |

| Table 4.  | I/O status in battery backup . . . . .                                                        | 15 |

| Table 5.  | Absolute maximum ratings . . . . .                                                            | 30 |

| Table 6.  | Operating and AC measurement conditions . . . . .                                             | 31 |

| Table 7.  | DC and AC characteristics . . . . .                                                           | 32 |

| Table 8.  | SO8 - 8-lead plastic small outline, 150 mils body width,<br>package mechanical data . . . . . | 37 |

| Table 9.  | TSSOP8 - 8-lead, thin shrink small outline, 3 x 3 mm body size, mechanical data . . . . .     | 38 |

| Table 10. | Ordering information scheme . . . . .                                                         | 39 |

| Table 11. | Marking description . . . . .                                                                 | 40 |

| Table 12. | Document revision history . . . . .                                                           | 41 |

## List of figures

|            |                                                                                                  |    |

|------------|--------------------------------------------------------------------------------------------------|----|

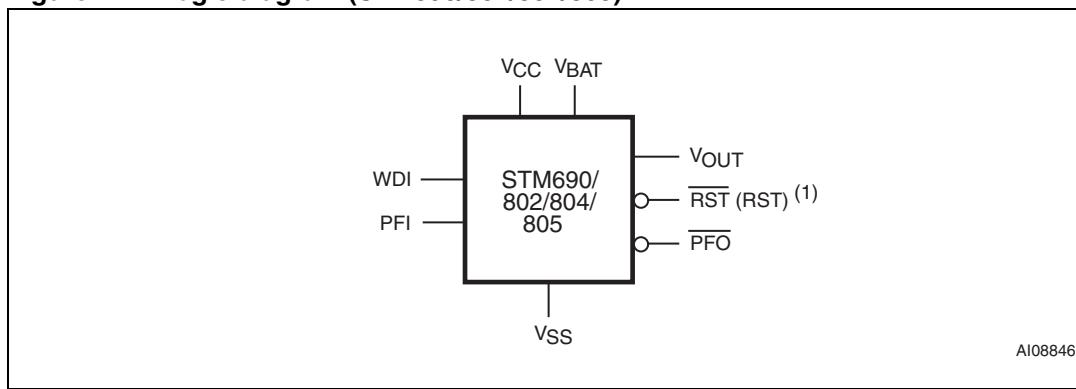

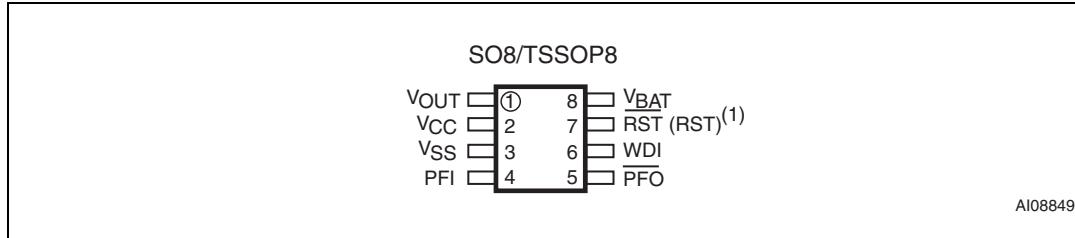

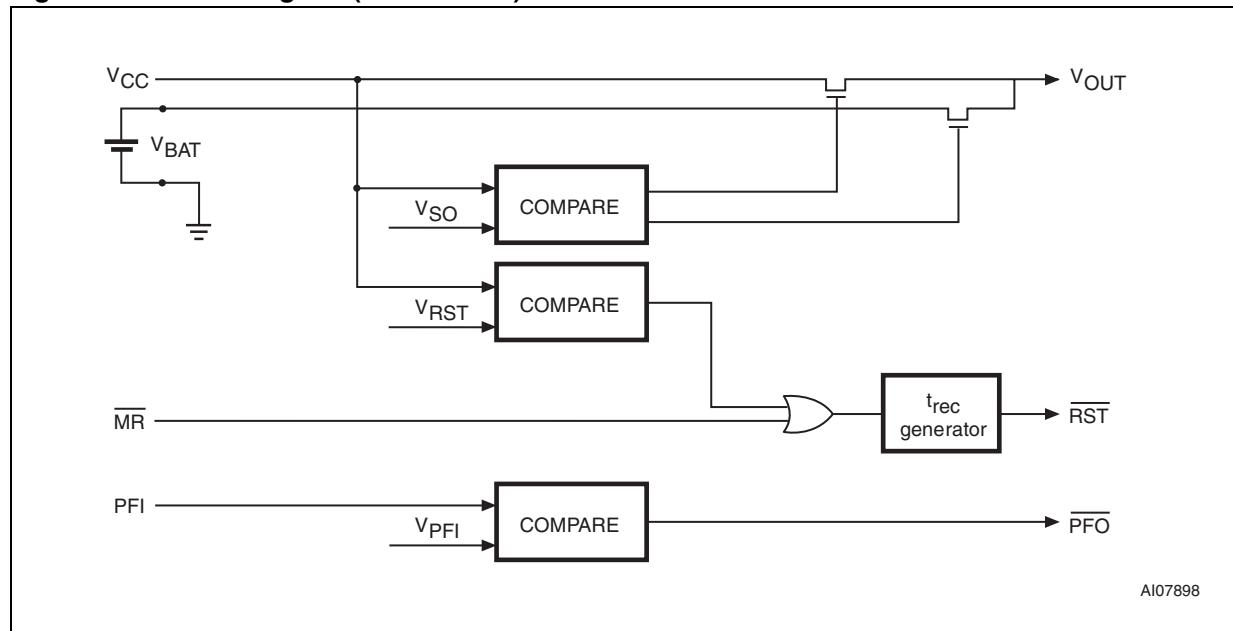

| Figure 1.  | Logic diagram (STM690/802/804/805) . . . . .                                                     | 6  |

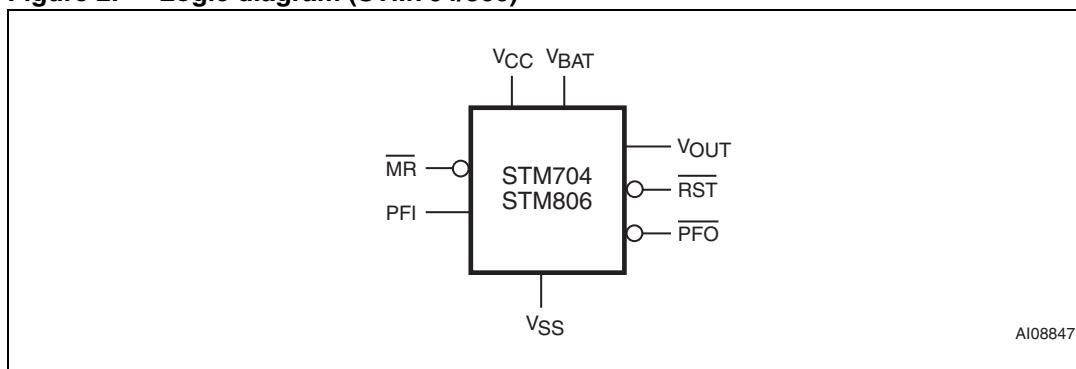

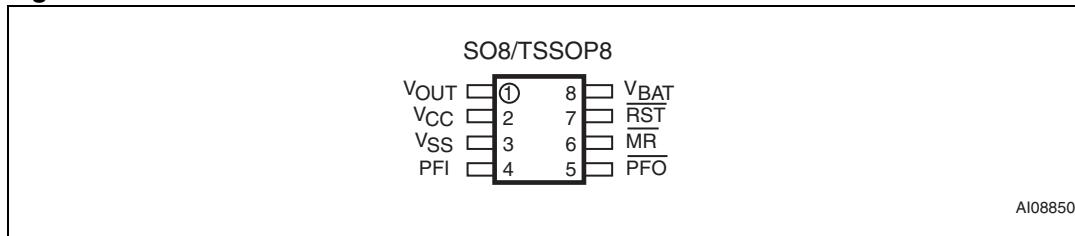

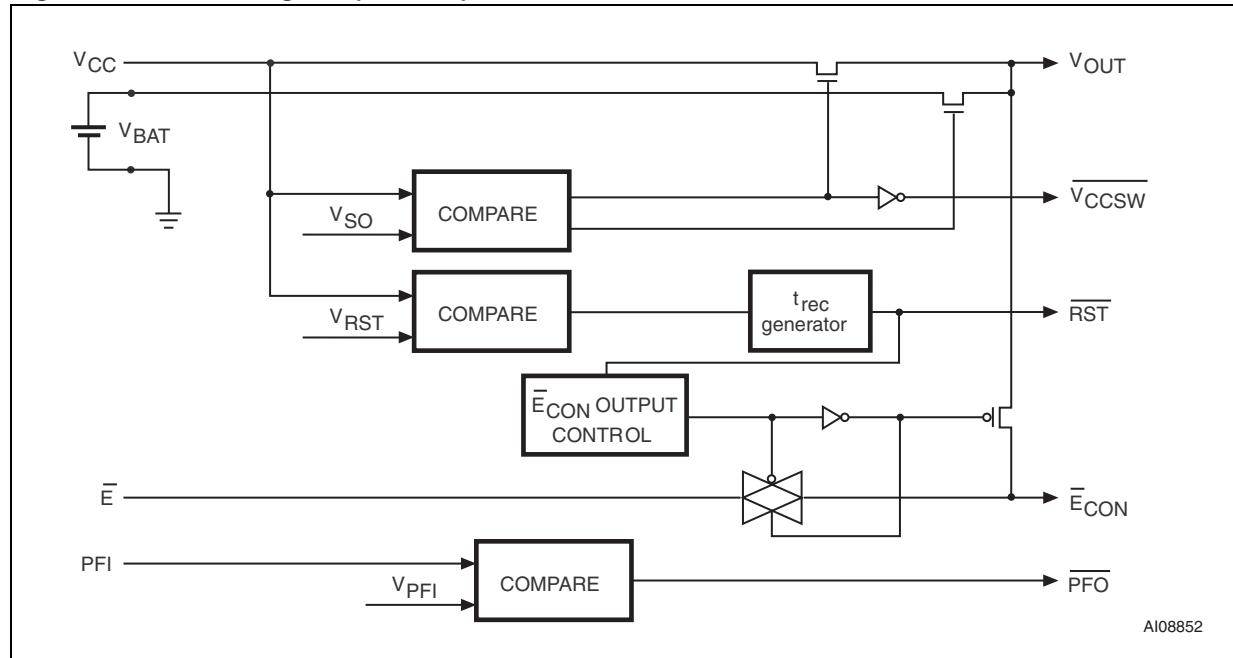

| Figure 2.  | Logic diagram (STM704/806) . . . . .                                                             | 6  |

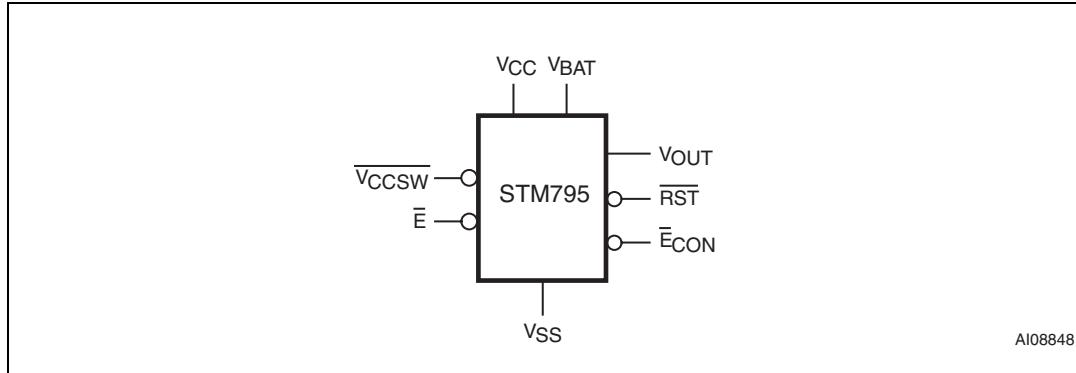

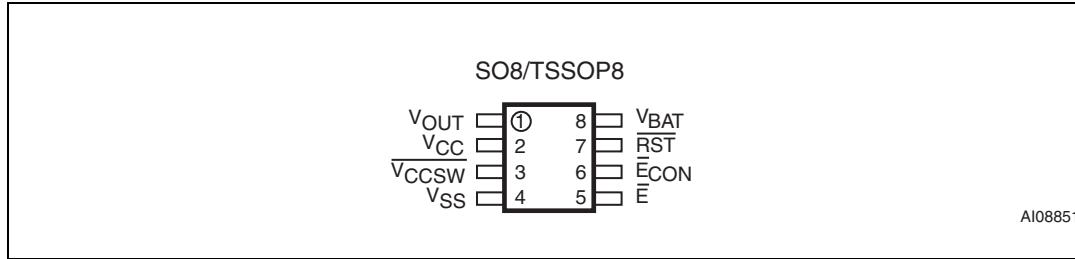

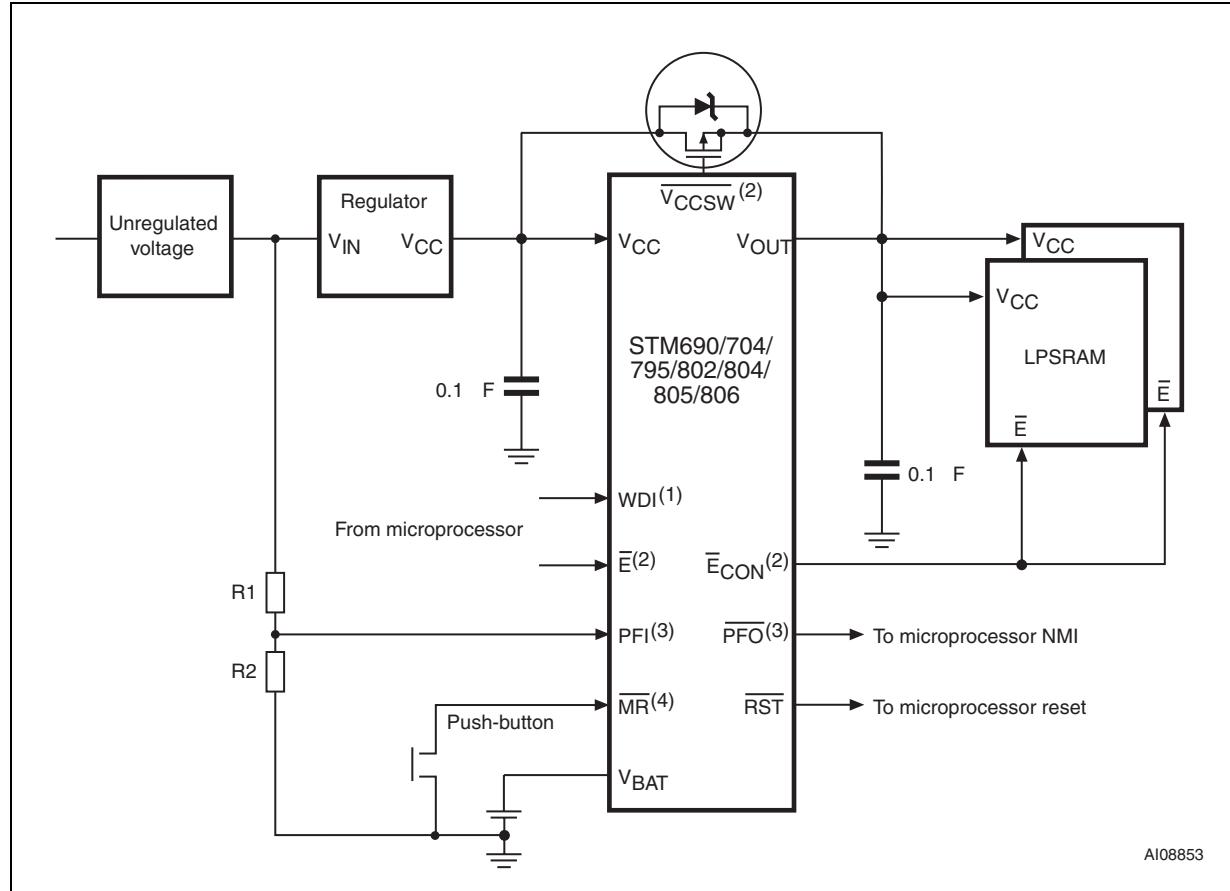

| Figure 3.  | Logic diagram (STM795) . . . . .                                                                 | 7  |

| Figure 4.  | STM690/802/804/805 connections . . . . .                                                         | 8  |

| Figure 5.  | STM704/806 connections . . . . .                                                                 | 8  |

| Figure 6.  | STM795 connections . . . . .                                                                     | 8  |

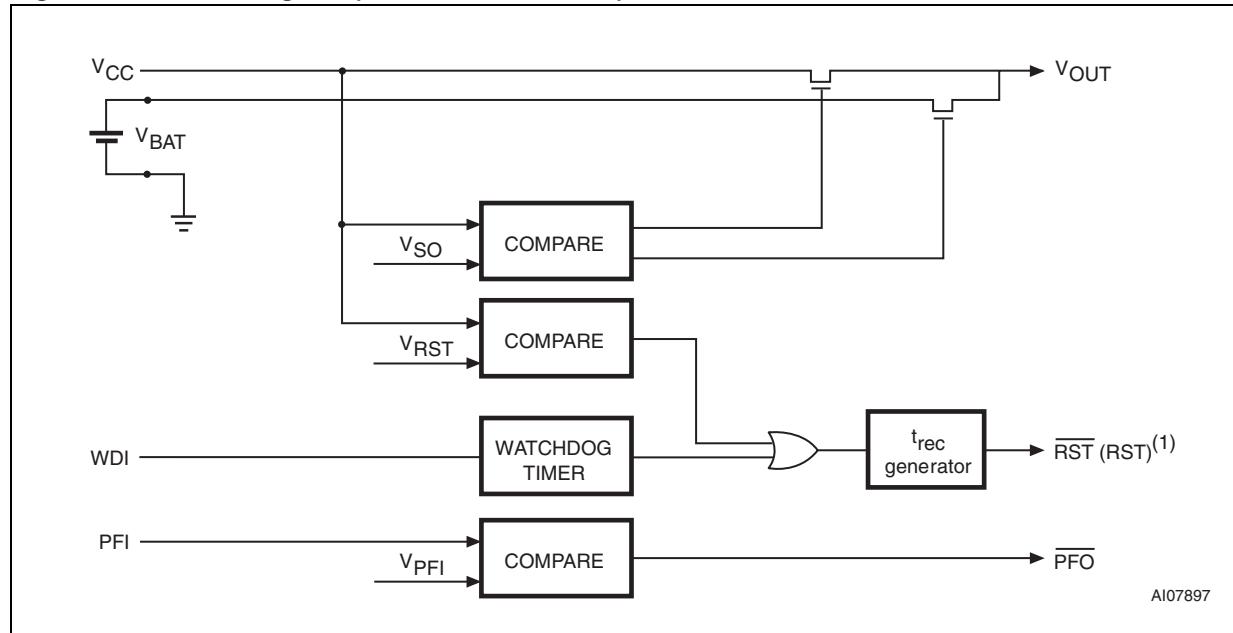

| Figure 7.  | Block diagram (STM690/802/804/805) . . . . .                                                     | 11 |

| Figure 8.  | Block diagram (STM704/806) . . . . .                                                             | 11 |

| Figure 9.  | Block diagram (STM795) . . . . .                                                                 | 12 |

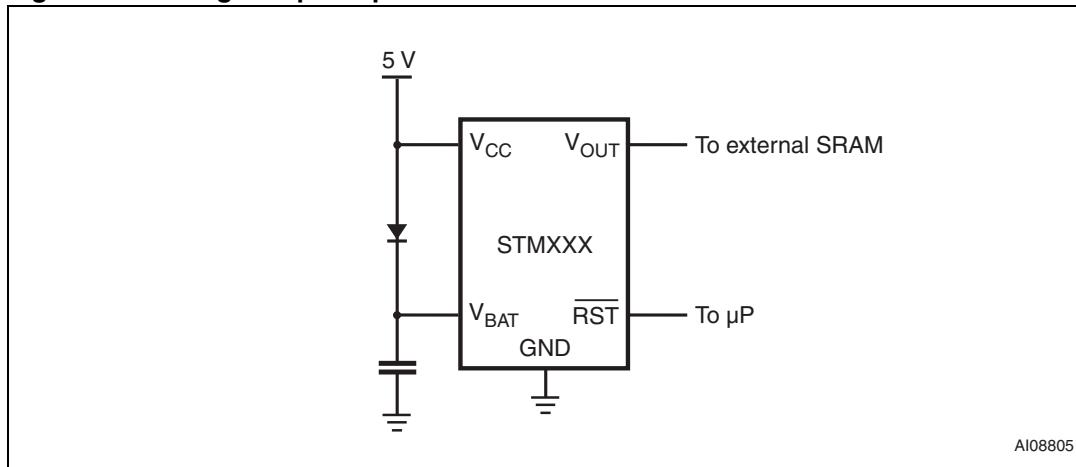

| Figure 10. | Hardware hookup . . . . .                                                                        | 13 |

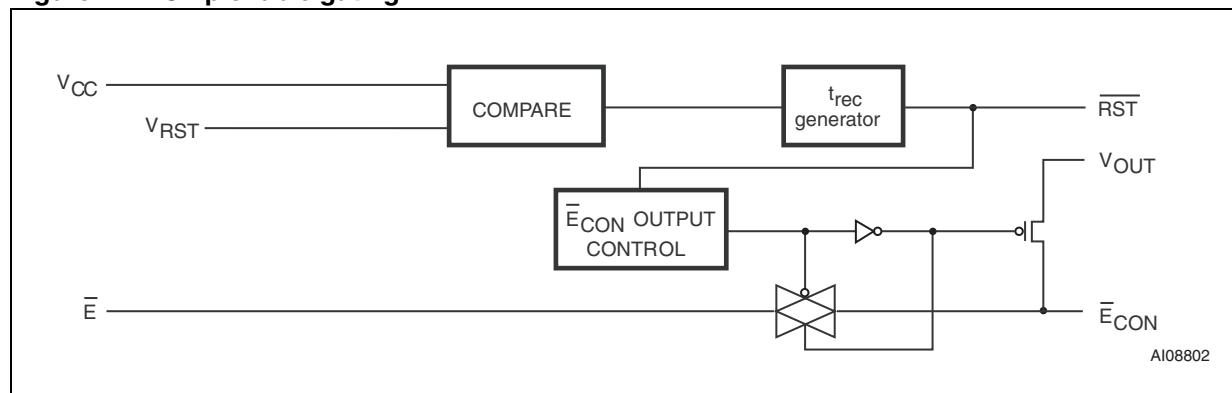

| Figure 11. | Chip enable gating . . . . .                                                                     | 16 |

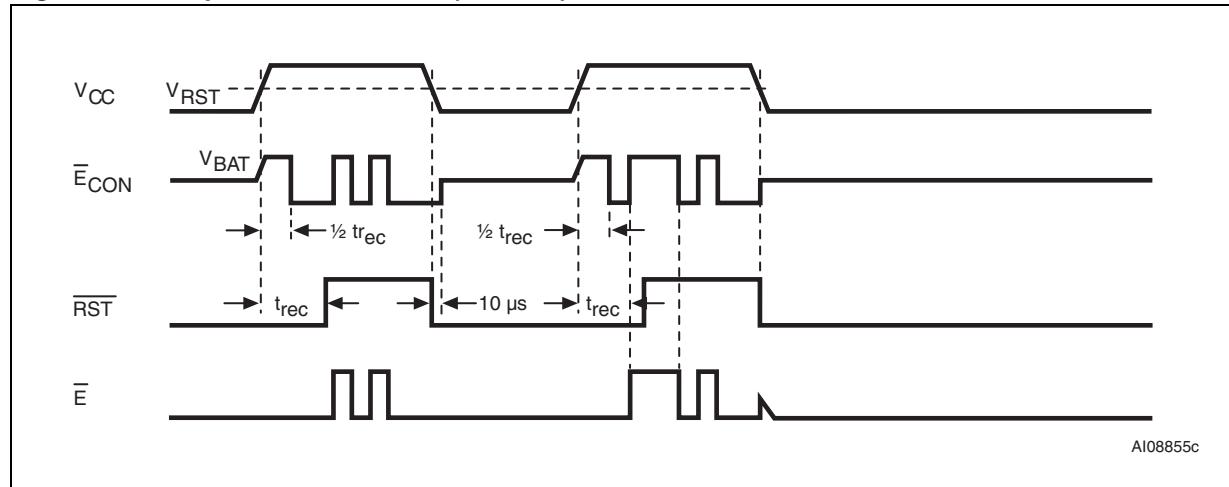

| Figure 12. | Chip enable waveform (STM795) . . . . .                                                          | 17 |

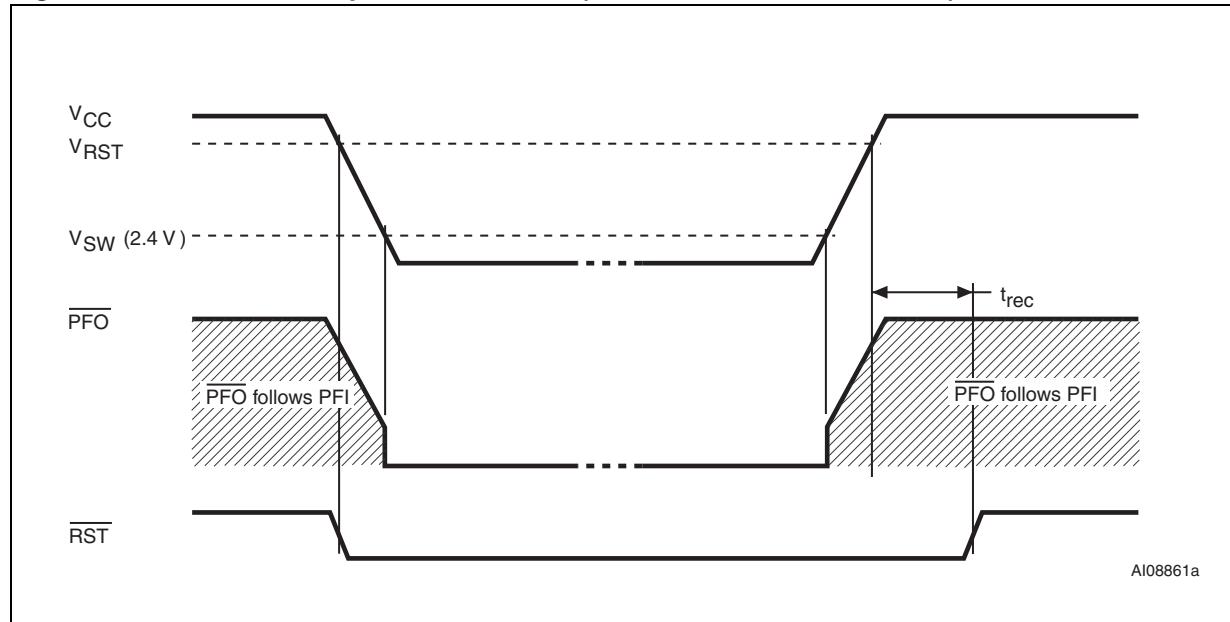

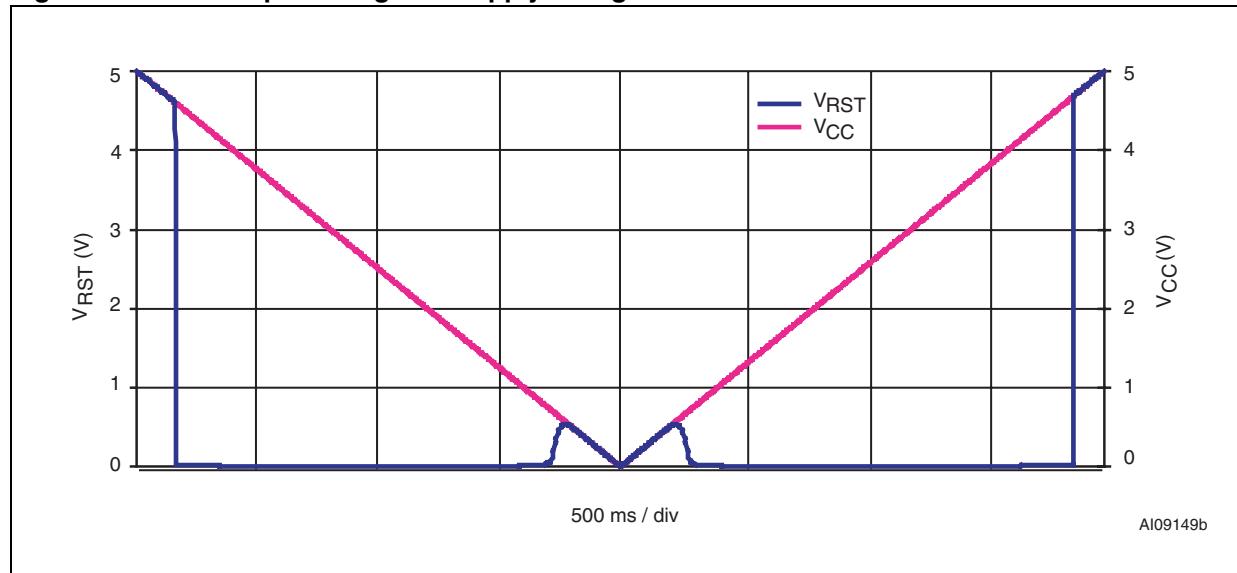

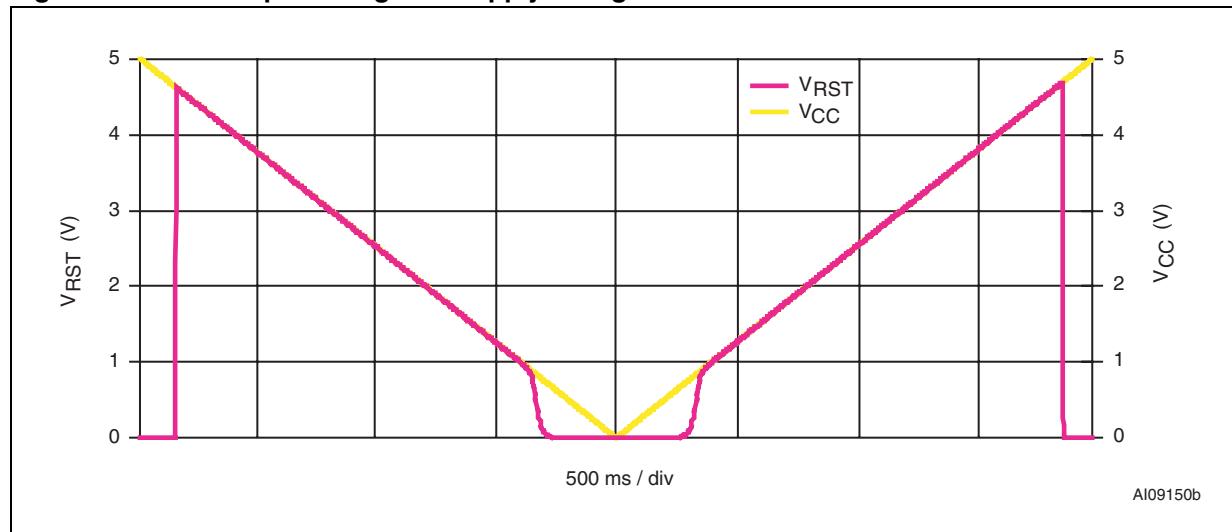

| Figure 13. | Power-fail comparator waveform (STM690/704/802/804/805/806) . . . . .                            | 18 |

| Figure 14. | Using a SuperCap™ . . . . .                                                                      | 19 |

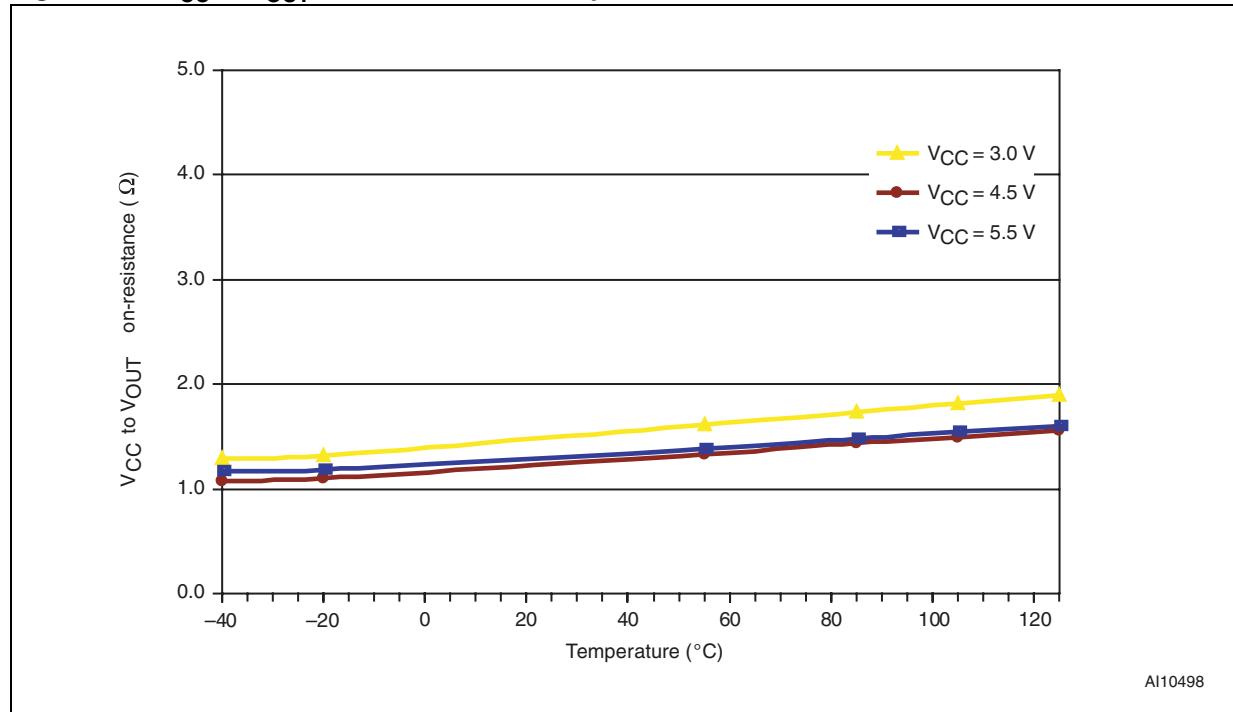

| Figure 15. | $V_{CC}$ to $V_{OUT}$ on-resistance vs. temperature . . . . .                                    | 20 |

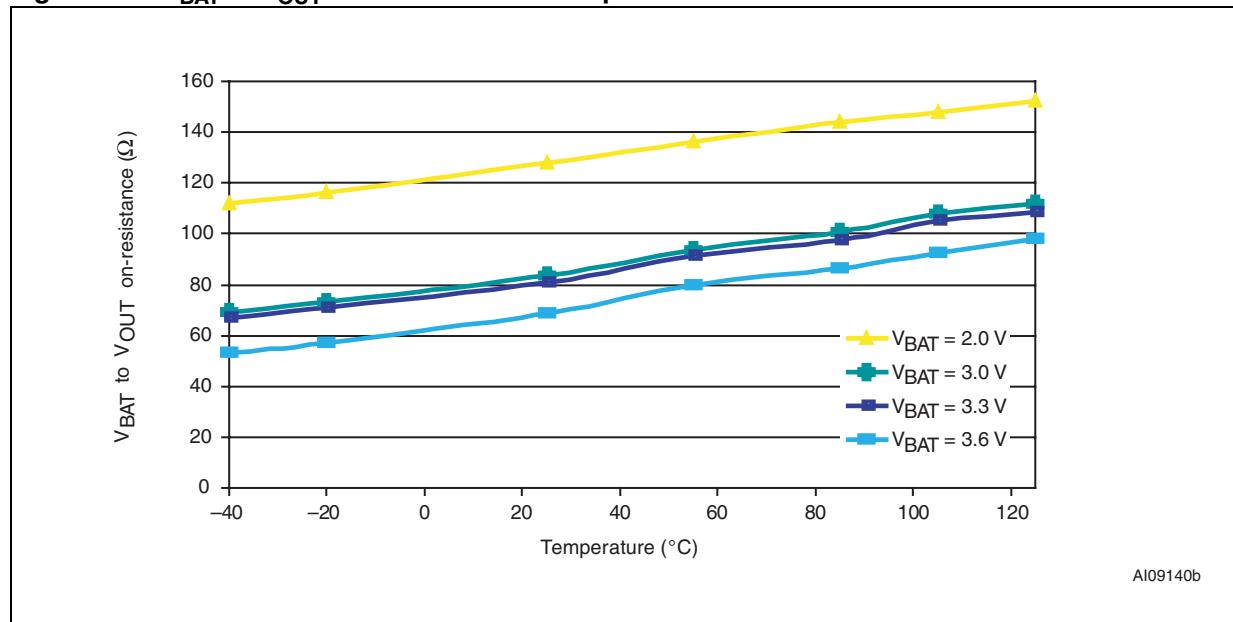

| Figure 16. | $V_{BAT}$ to $V_{OUT}$ on-resistance vs. temperature . . . . .                                   | 20 |

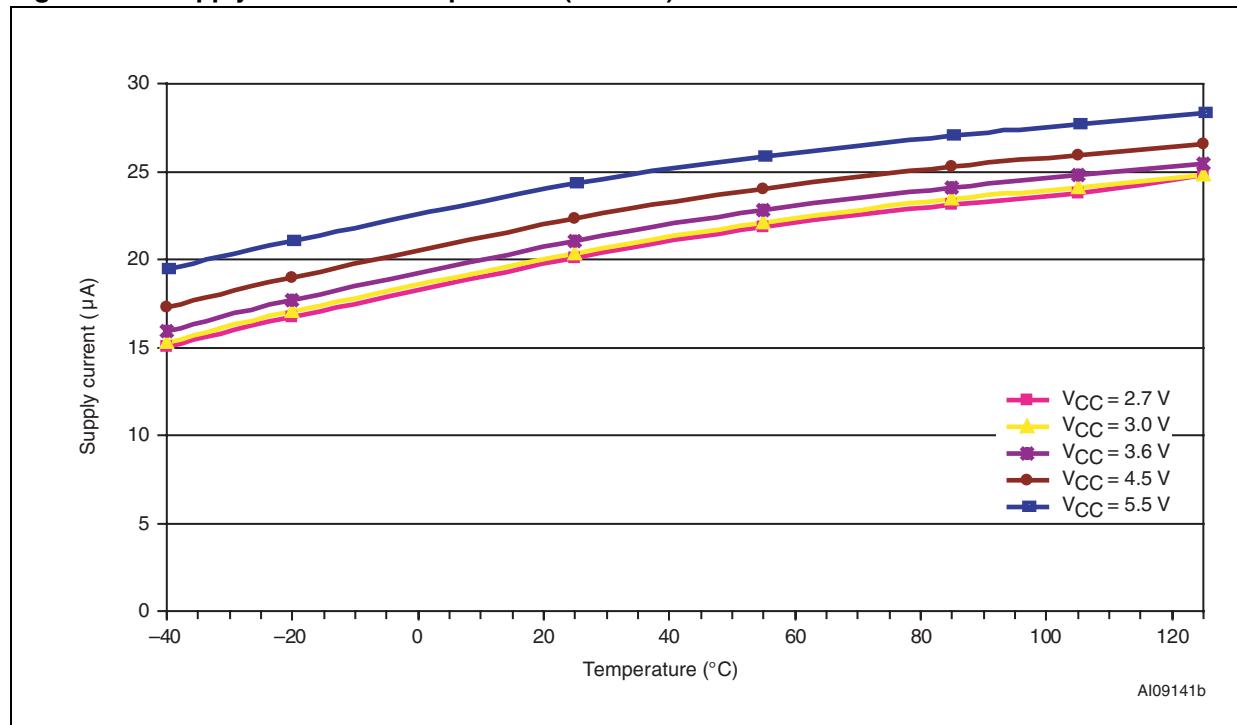

| Figure 17. | Supply current vs. temperature (no load) . . . . .                                               | 21 |

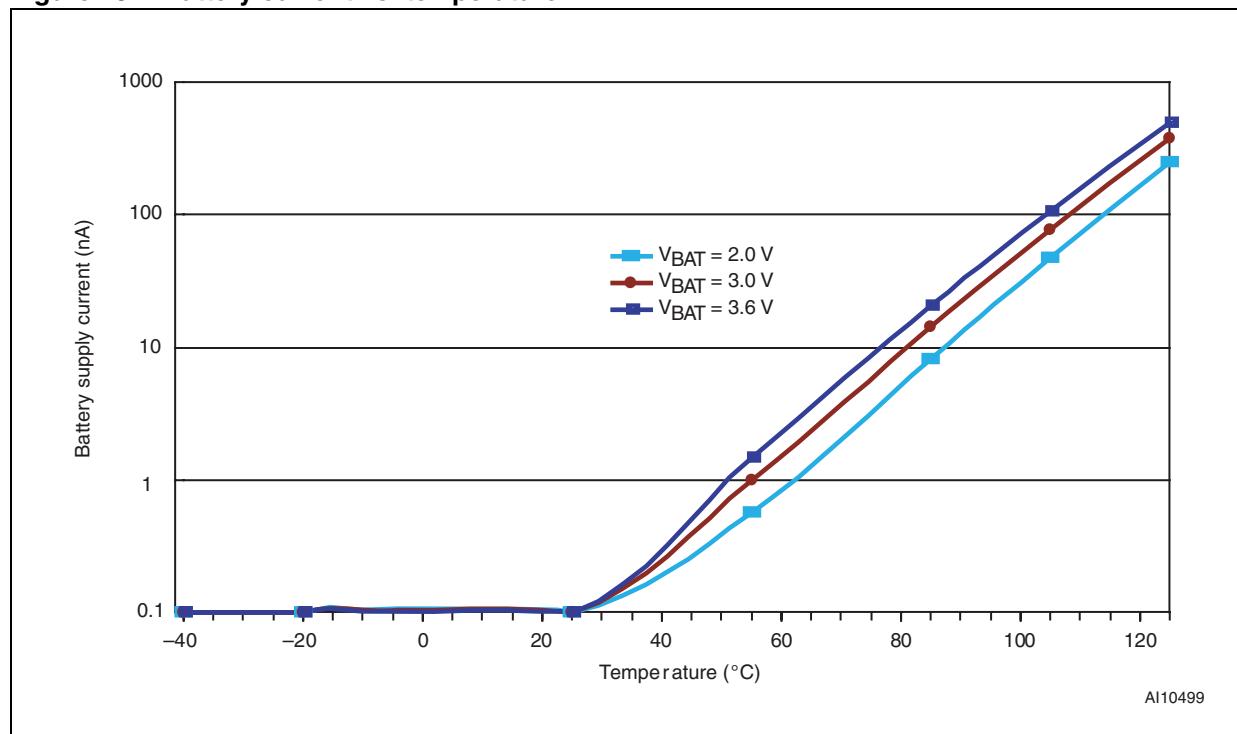

| Figure 18. | Battery current vs. temperature . . . . .                                                        | 21 |

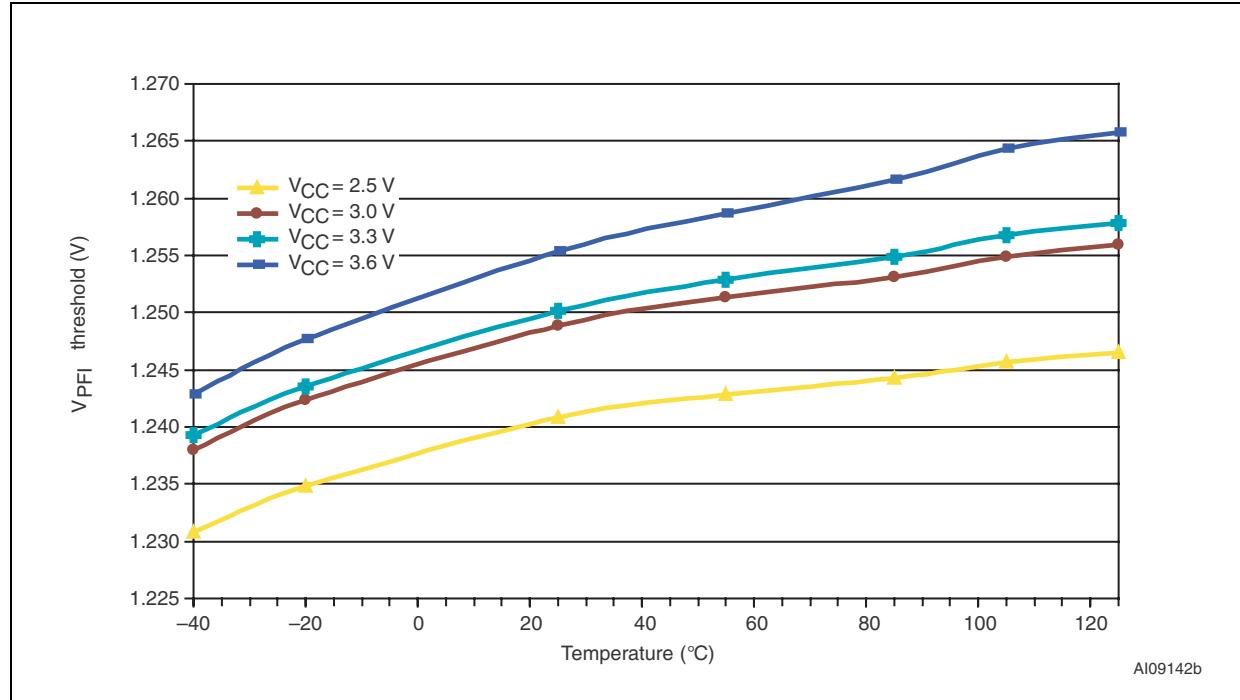

| Figure 19. | $V_{PFI}$ threshold vs. temperature . . . . .                                                    | 22 |

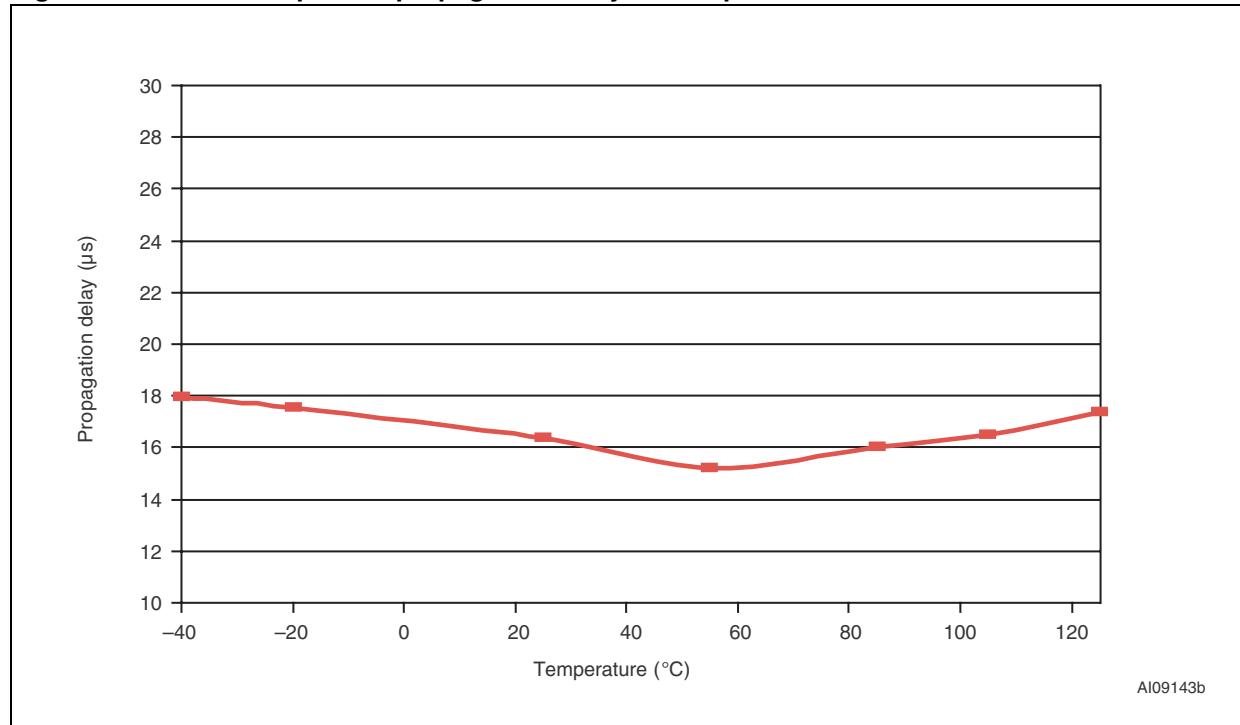

| Figure 20. | Reset comparator propagation delay vs. temperature . . . . .                                     | 22 |

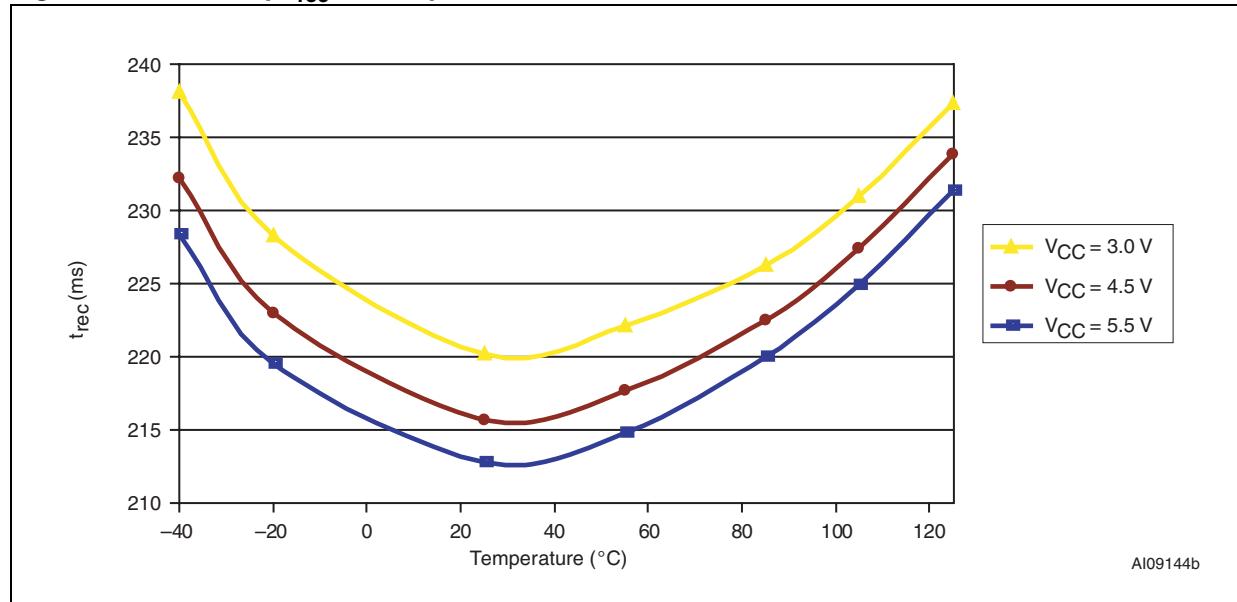

| Figure 21. | Power-up $t_{rec}$ vs. temperature . . . . .                                                     | 23 |

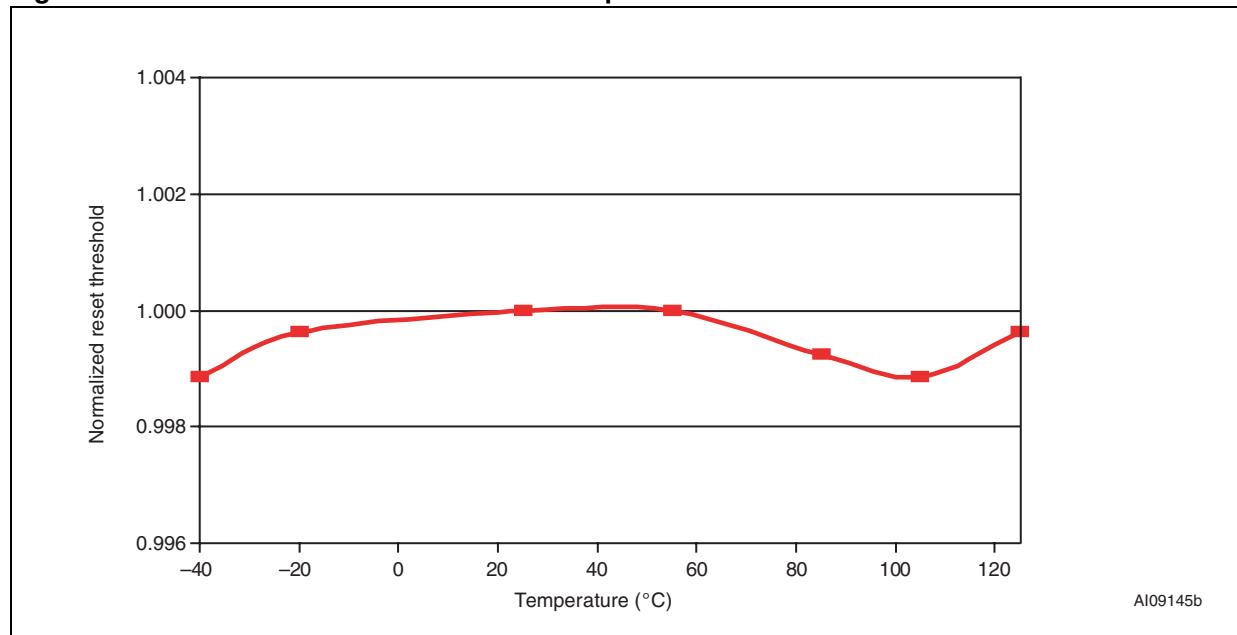

| Figure 22. | Normalized reset threshold vs. temperature . . . . .                                             | 23 |

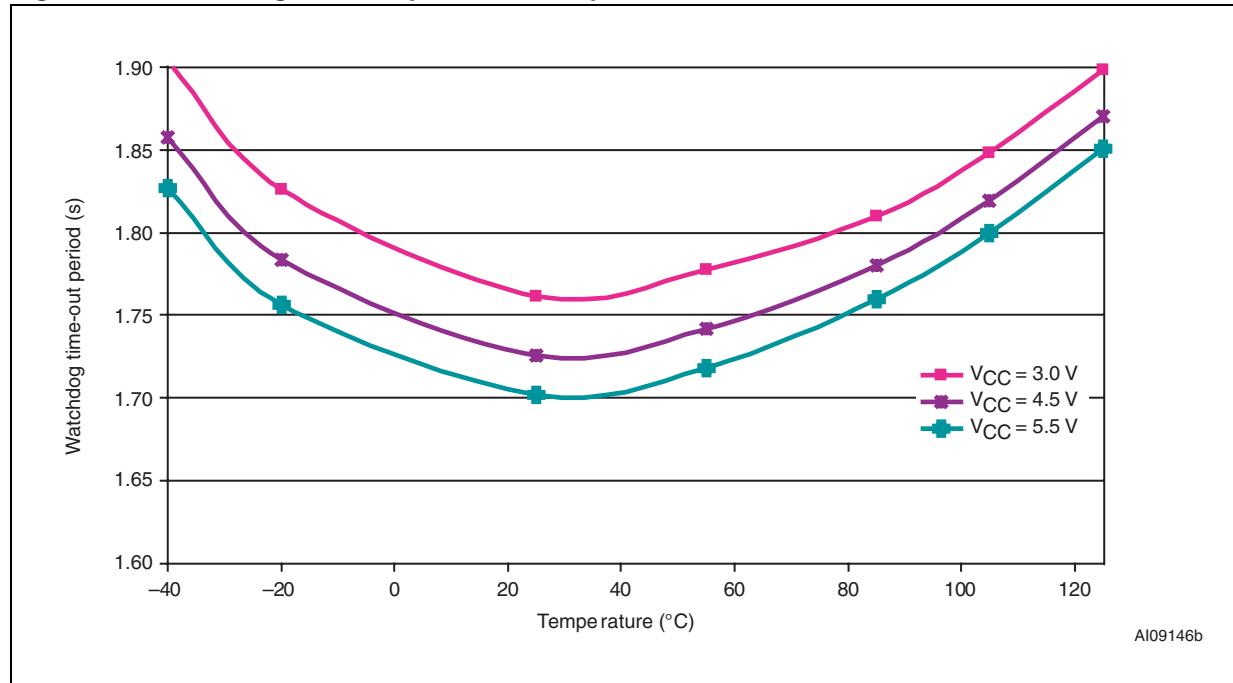

| Figure 23. | Watchdog time-out period vs. temperature . . . . .                                               | 24 |

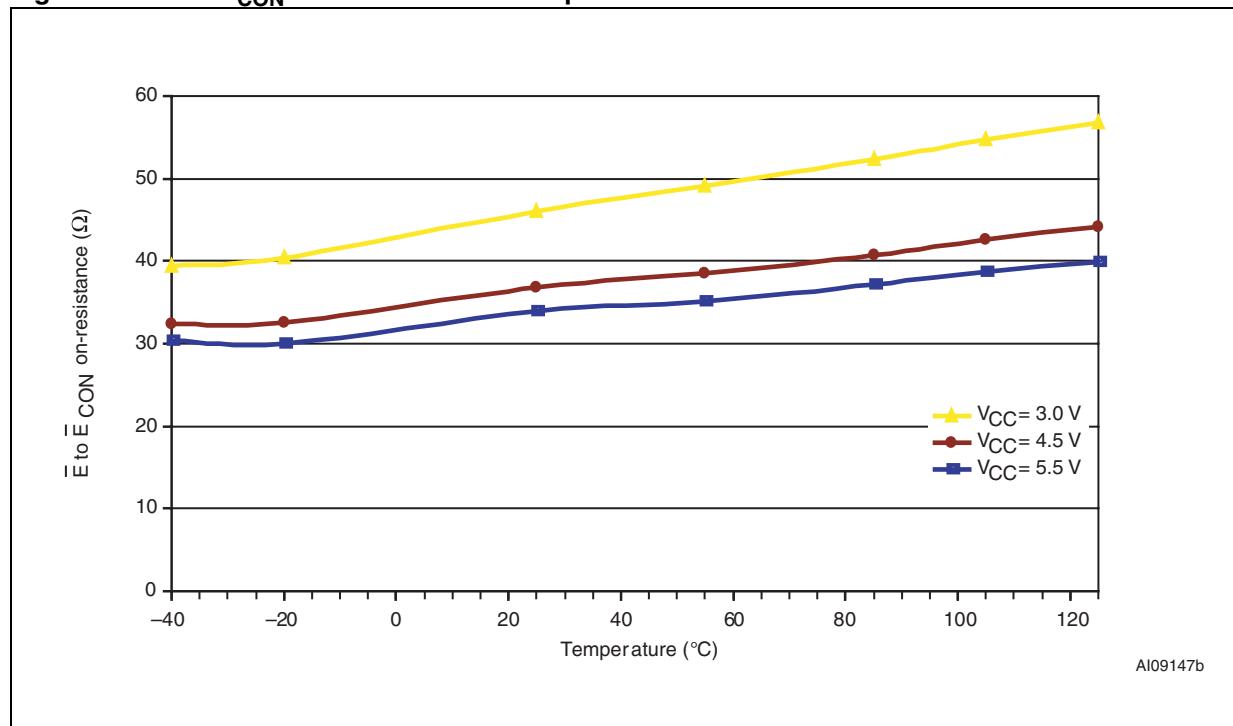

| Figure 24. | $\bar{E}$ to $\bar{E}_{CON}$ on-resistance vs. temperature . . . . .                             | 24 |

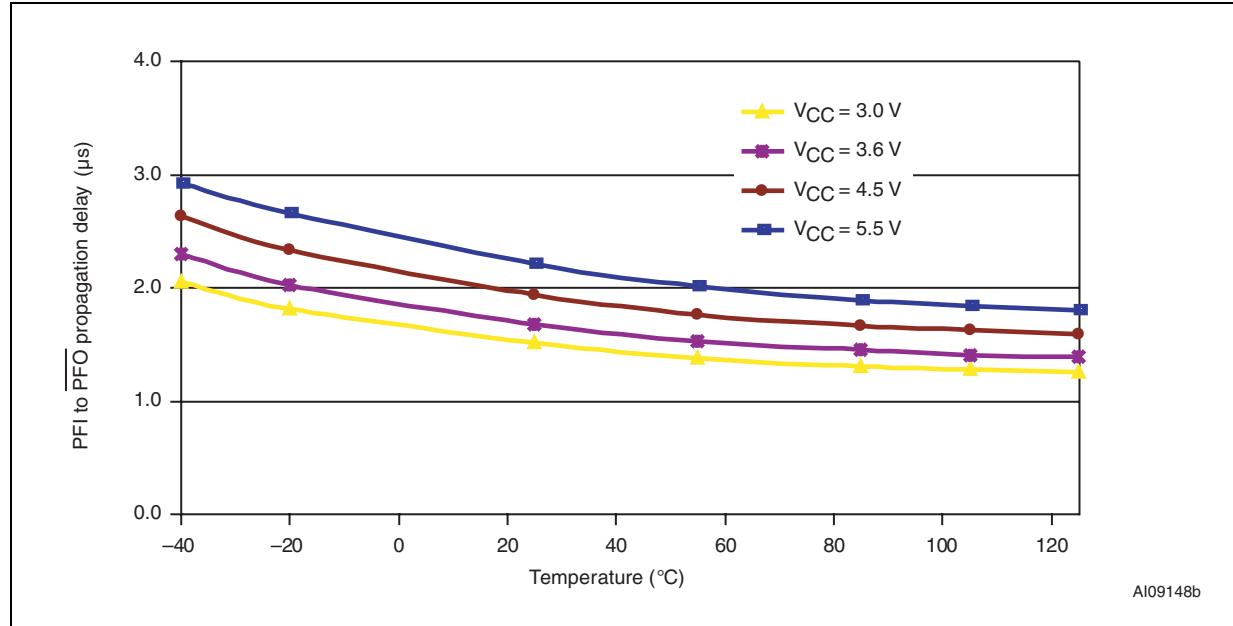

| Figure 25. | PFI to PFO propagation delay vs. temperature . . . . .                                           | 25 |

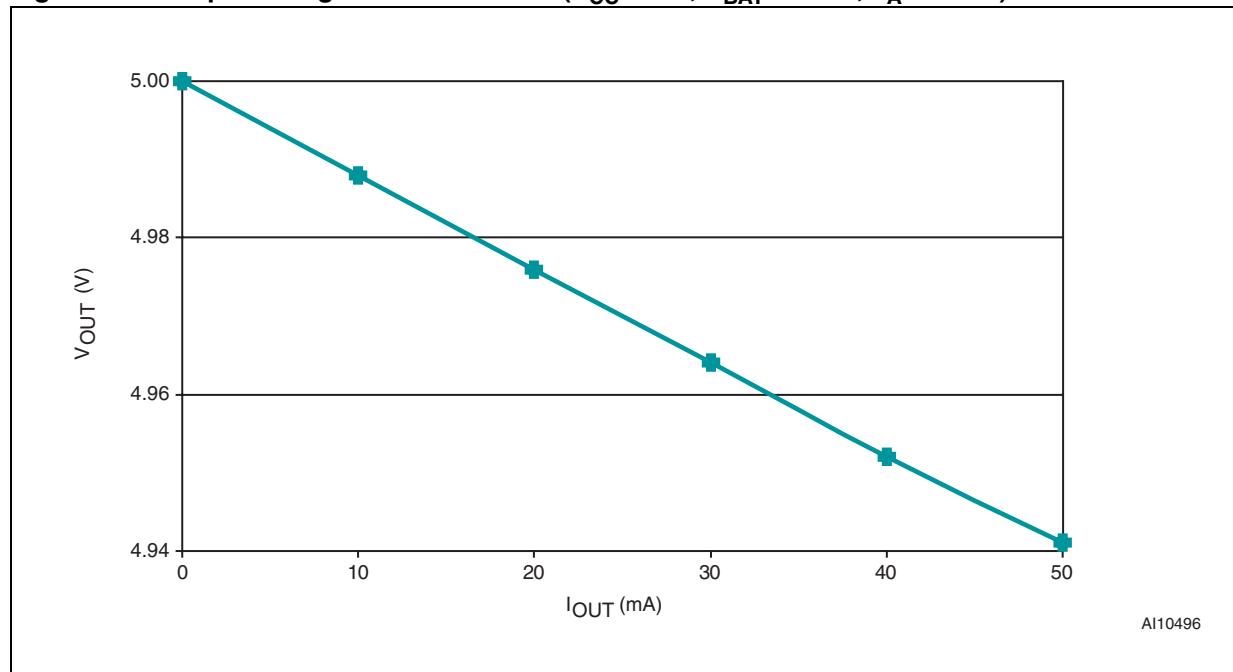

| Figure 26. | Output voltage vs. load current ( $V_{CC} = 5$ V; $V_{BAT} = 2.8$ V; $T_A = 25$ °C) . . . . .    | 25 |

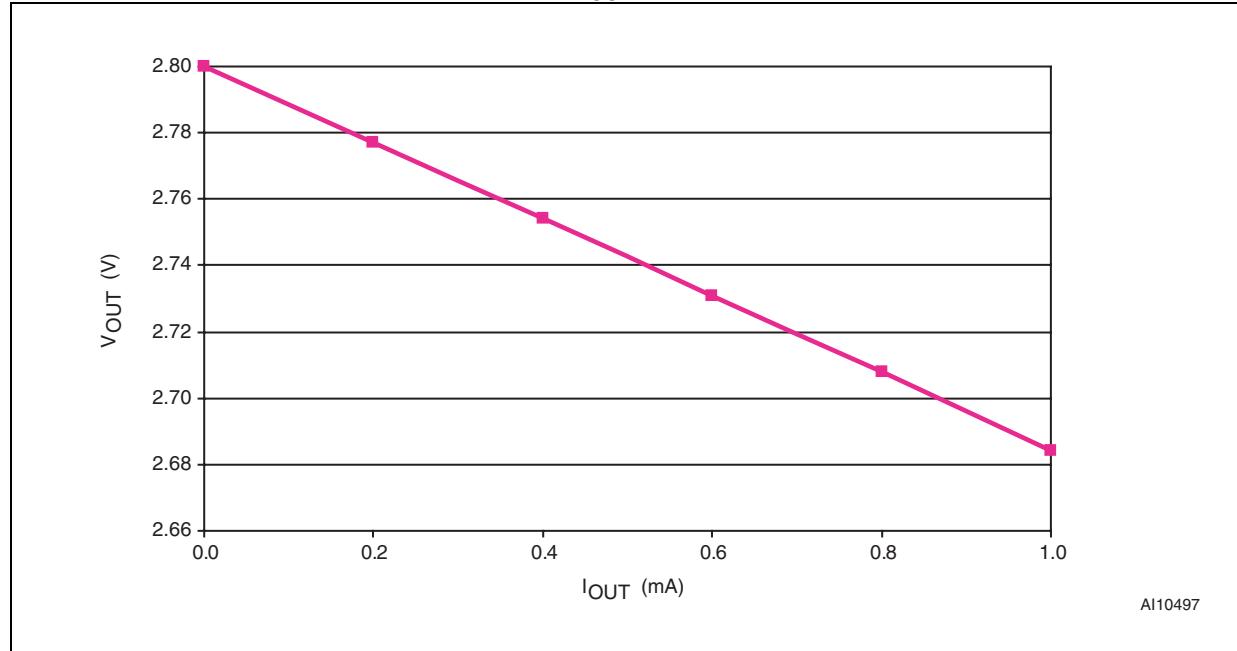

| Figure 27. | Output voltage vs. load current ( $V_{CC} = 0$ V; $V_{BAT} = 2.8$ V; $T_A = 25$ °C) . . . . .    | 26 |

| Figure 28. | $\bar{RST}$ output voltage vs. supply voltage . . . . .                                          | 26 |

| Figure 29. | RST output voltage vs. supply voltage . . . . .                                                  | 27 |

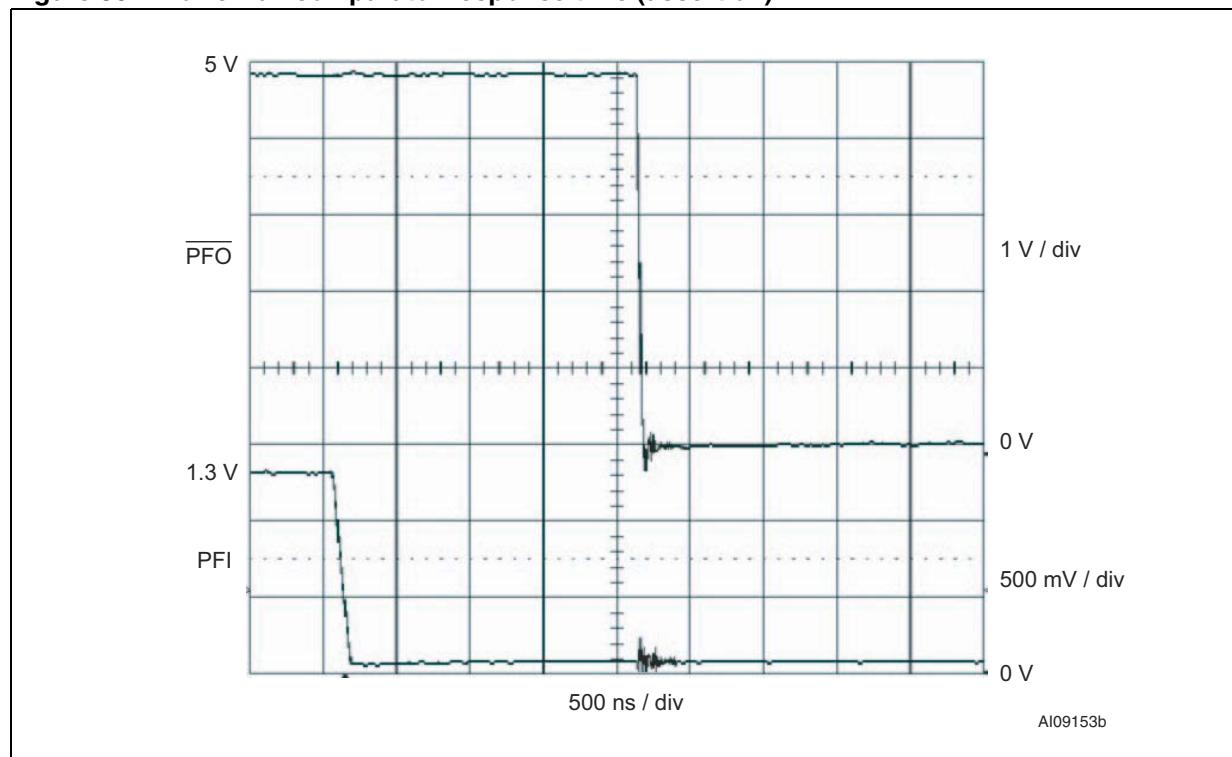

| Figure 30. | Power-fail comparator response time (assertion) . . . . .                                        | 27 |

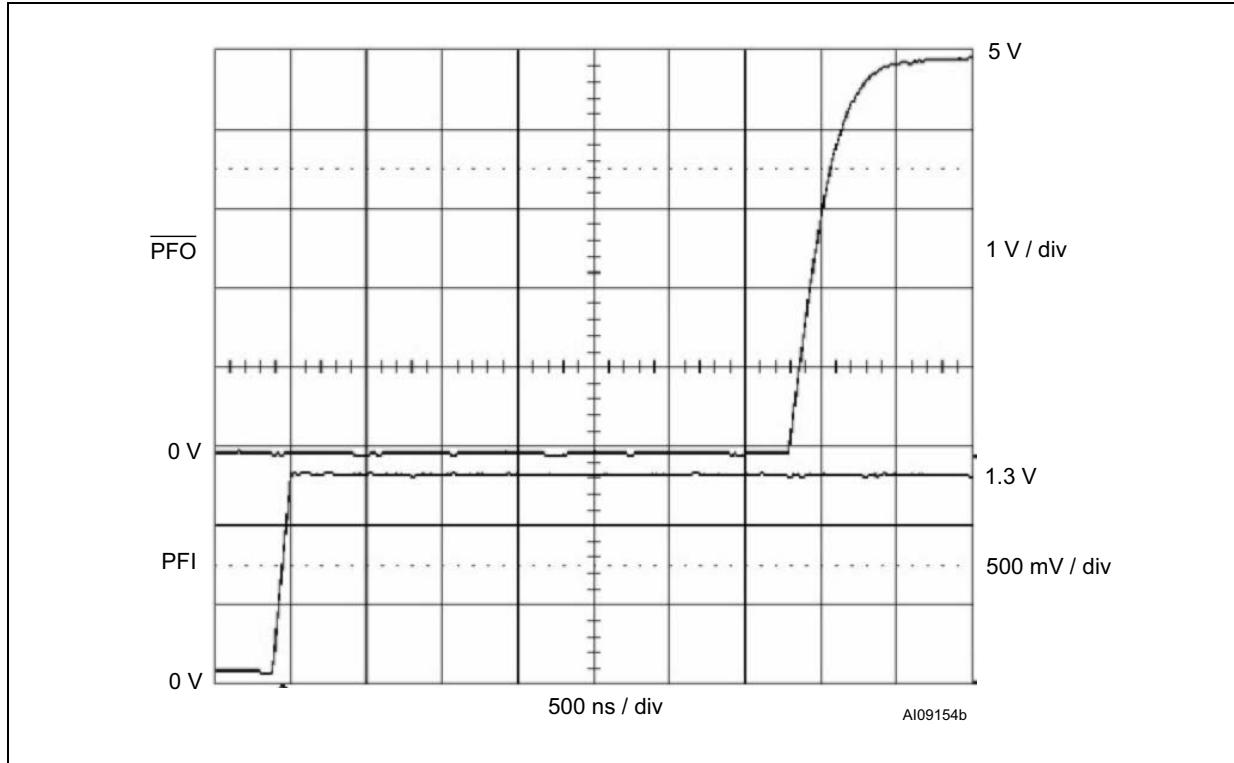

| Figure 31. | Power-fail comparator response time (de-assertion) . . . . .                                     | 28 |

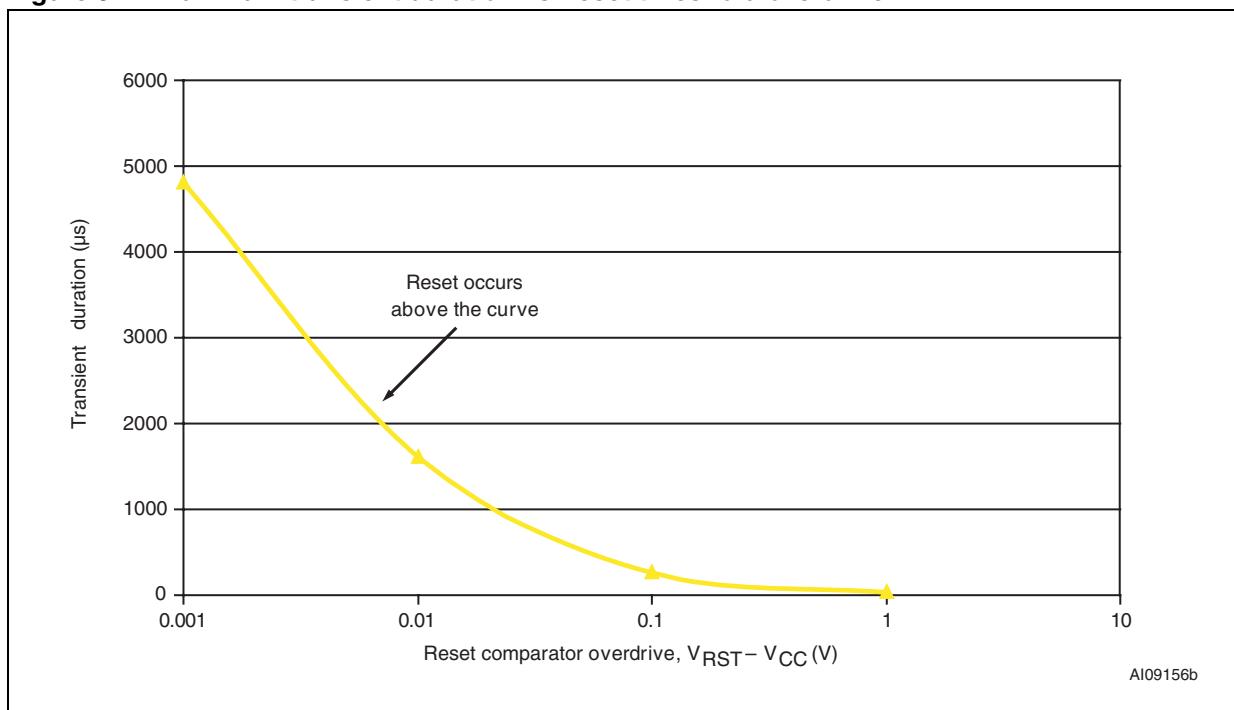

| Figure 32. | Maximum transient duration vs. reset threshold overdrive . . . . .                               | 28 |

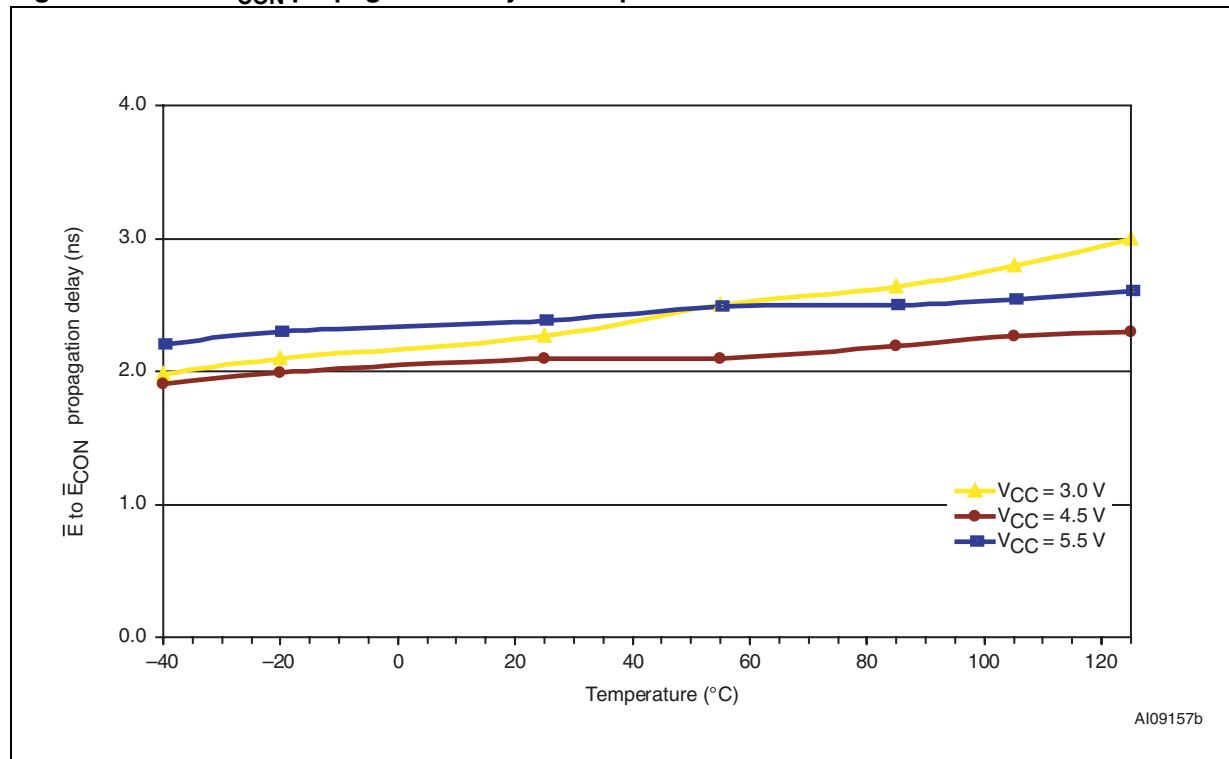

| Figure 33. | $\bar{E}$ to $\bar{E}_{CON}$ propagation delay vs. temperature . . . . .                         | 29 |

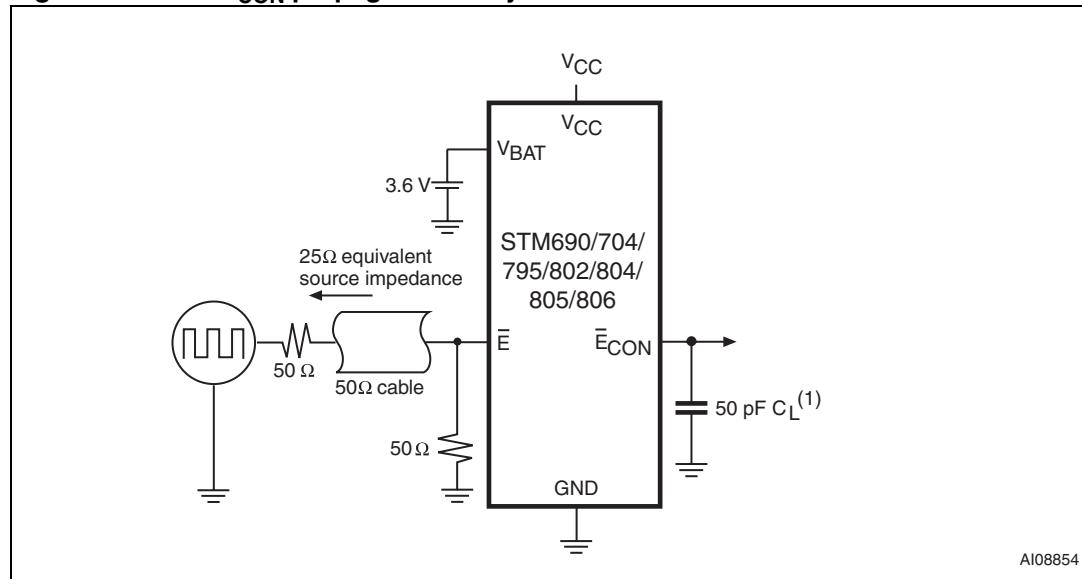

| Figure 34. | $\bar{E}$ to $\bar{E}_{CON}$ propagation delay test circuit . . . . .                            | 31 |

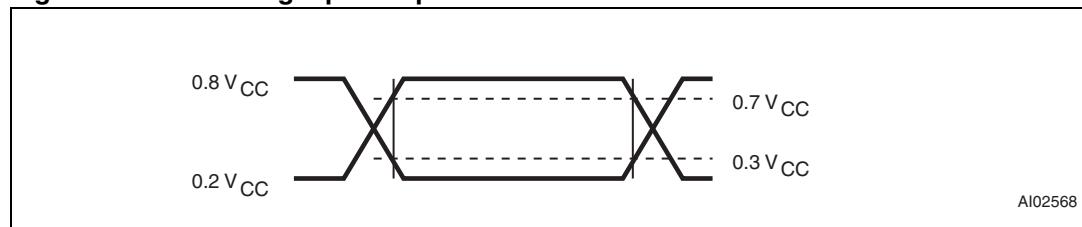

| Figure 35. | AC testing input/output waveforms . . . . .                                                      | 31 |

| Figure 36. | $MR$ timing waveform . . . . .                                                                   | 32 |

| Figure 37. | Watchdog timing . . . . .                                                                        | 32 |

| Figure 38. | SO8 – 8-lead plastic small outline, 150 mils body width,<br>package mechanical drawing . . . . . | 37 |

| Figure 39. | TSSOP8 – 8-lead, thin shrink small outline, 3 x 3 mm body size, outline . . . . .                | 38 |

## 1 Description

The STM690/704/795/802/804/805/806 supervisors are self-contained devices which provide microprocessor supervisory functions with the ability to non-volatile write-protect external LPSRAM. A precision voltage reference and comparator monitors the  $V_{CC}$  input for an out-of-tolerance condition. When an invalid  $V_{CC}$  condition occurs, the reset output ( $\overline{RST}$ ) is forced low (or high in the case of RST). These devices also offer a watchdog timer (except for STM704/795/806) as well as a power-fail comparator (except for STM795) to provide the system with an early warning of impending power failure.

These devices are available in a standard 8-pin SOIC package or a space-saving 8-pin TSSOP package.

**Figure 1. Logic diagram (STM690/802/804/805)**

1. For STM804/805, reset output is active-high and open drain.

**Figure 2. Logic diagram (STM704/806)**

**Figure 3. Logic diagram (STM795)****Table 2. Signal names**

|                             |                                |

|-----------------------------|--------------------------------|

| $\overline{MR}$             | Push-button reset input        |

| WDI                         | Watchdog input                 |

| $\overline{RST}$            | Active-low reset output        |

| $RST^{(1)}$                 | Active-high reset output       |

| $\overline{E}^{(2)}$        | Chip enable input              |

| $\overline{E}_{CON}^{(2)}$  | Conditioned chip enable output |

| $\overline{V_{CCSW}}^{(2)}$ | $V_{CC}$ switch output         |

| $V_{OUT}$                   | Supply voltage output          |

| $V_{CC}$                    | Supply voltage                 |

| $V_{BAT}$                   | Backup supply voltage          |

| PFI                         | Power-fail input               |

| $\overline{PFO}$            | Power-fail output              |

| $V_{SS}$                    | Ground                         |

1. Open drain for STM804/805 only.

2. STM795.

**Figure 4. STM690/802/804/805 connections**

1. For STM804/805, reset output is active-high and open drain.

**Figure 5. STM704/806 connections****Figure 6. STM795 connections**

## 1.1 Pin descriptions

### 1.1.1 $\overline{MR}$ (manual reset)

A logic low on  $\overline{MR}$  asserts the reset output. Reset remains asserted as long as  $\overline{MR}$  is low and for  $t_{rec}$  after  $\overline{MR}$  returns high. This active-low input has an internal pull-up. It can be driven from a TTL or CMOS logic line, or shorted to ground with a switch. Leave open if unused.

### 1.1.2 WDI (watchdog input)

If WDI remains high or low for 1.6 s, the internal watchdog timer runs out and reset is triggered. The internal watchdog timer clears while reset is asserted or when WDI sees a rising or falling edge.

The watchdog function cannot be disabled by allowing the WDI pin to float.

### 1.1.3 $\overline{RST}$ (active-low reset)

Pulses low for  $t_{rec}$  when triggered, and stays low whenever  $V_{CC}$  is below the reset threshold or when  $\overline{MR}$  is a logic low. It remains low for  $t_{rec}$  after either  $V_{CC}$  rises above the reset threshold, the watchdog triggers a reset, or  $\overline{MR}$  goes from low to high.

### 1.1.4 RST (active-high reset - open drain)

Pulses high for  $t_{rec}$  when triggered, and stays high whenever  $V_{CC}$  is above the reset threshold or when  $\overline{MR}$  is a logic high. It remains high for  $t_{rec}$  after either  $V_{CC}$  falls below the reset threshold, the watchdog triggers a reset, or  $\overline{MR}$  goes from high to low.

### 1.1.5 PFI (power-fail input)

When PFI is less than  $V_{PFI}$  or when  $V_{CC}$  falls below  $V_{SW}$  (2.4 V),  $\overline{PFO}$  goes low; otherwise,  $\overline{PFO}$  remains high. Connect to ground if unused.

### 1.1.6 $\overline{PFO}$ (power-fail output)

When PFI is less than  $V_{PFI}$ , or  $V_{CC}$  falls below  $V_{SW}$ ,  $\overline{PFO}$  goes low; otherwise,  $\overline{PFO}$  remains high. Leave open if unused. Output type is push-pull.

### 1.1.7 $V_{OUT}$ (supply output voltage)

When  $V_{CC}$  is above the switchover voltage ( $V_{SO}$ ),  $V_{OUT}$  is connected to  $V_{CC}$  through a P-channel MOSFET switch. When  $V_{CC}$  falls below  $V_{SO}$ ,  $V_{BAT}$  connects to  $V_{OUT}$ . Connect to  $V_{CC}$  if no battery is used.

### 1.1.8 $\overline{Vccsw}$ ( $V_{CC}$ switch output)

When  $V_{OUT}$  switches to battery,  $\overline{Vccsw}$  is high. When  $V_{OUT}$  switches back to  $V_{CC}$ ,  $\overline{Vccsw}$  is low. It can be used to drive gate of external PMOS transistor for  $I_{OUT}$  requirements exceeding 75 mA. Output type is push-pull.

**1.1.9  $\bar{E}$  (chip enable input)**

The input to the chip enable gating circuit. Connect to ground if unused.

**1.1.10  $\bar{E}_{CON}$  (conditional chip enable)**

$\bar{E}_{CON}$  goes low only when  $\bar{E}$  is low and reset is not asserted. If  $\bar{E}_{CON}$  is low when reset is asserted,  $\bar{E}_{CON}$  will remain low for 15  $\mu$ s or until  $\bar{E}$  goes high, whichever occurs first. In the disabled mode,  $\bar{E}_{CON}$  is pulled up to  $V_{OUT}$ .

**1.1.11  $V_{BAT}$  (backup battery input)**

When  $V_{CC}$  falls below  $V_{SO}$ ,  $V_{OUT}$  switches from  $V_{CC}$  to  $V_{BAT}$ . When  $V_{CC}$  rises above  $V_{SO}$  + hysteresis,  $V_{OUT}$  reconnects to  $V_{CC}$ .  $V_{BAT}$  may exceed  $V_{CC}$ . Connect to  $V_{CC}$  if no battery is used.

**Table 3. Pin description**

| Pin    |                  |                  |                  | Name             | Function                           |

|--------|------------------|------------------|------------------|------------------|------------------------------------|

| STM795 | STM690<br>STM802 | STM704<br>STM806 | STM804<br>STM805 |                  |                                    |

| —      | —                | 6                | —                | $\bar{MR}$       | Push-button reset input            |

| —      | 6                | —                | 6                | WDI              | Watchdog input                     |

| 7      | 7                | 7                | —                | $\bar{RST}$      | Active-low reset output            |

| —      | —                | —                | 7                | RST              | Active-high reset output           |

| —      | 4                | 4                | 4                | PFI              | Power-fail input                   |

| —      | 5                | 5                | 5                | $\bar{PFO}$      | Power-fail output (push-pull)      |

| 1      | 1                | 1                | 1                | $V_{OUT}$        | Supply output for external LPSRAM  |

| 2      | 2                | 2                | 2                | $V_{CC}$         | Supply voltage                     |

| 3      | —                | —                | —                | $\bar{V}_{CCSW}$ | $V_{CC}$ switch output (push-pull) |

| 4      | 3                | 3                | 3                | $V_{SS}$         | Ground                             |

| 5      | —                | —                | —                | $\bar{E}$        | Chip enable input                  |

| 6      | —                | —                | —                | $\bar{E}_{CON}$  | Conditioned chip enable output     |

| 8      | 8                | 8                | 8                | $V_{BAT}$        | Backup battery input               |

Figure 7. Block diagram (STM690/802/804/805)

1. For STM804/805, reset output is active-high and open drain.

Figure 8. Block diagram (STM704/806)

Figure 9. Block diagram (STM795)

Figure 10. Hardware hookup

1. For STM690/802/804/805.

2. For STM795 only.

3. Not available on STM795.

4. For STM704/806.

## 2 Operation

### 2.1 Reset output

The STM690/704/795/802/804/805/806 supervisor asserts a reset signal to the MCU whenever  $V_{CC}$  goes below the reset threshold ( $V_{RST}$ ), a watchdog time-out occurs, or when the push-button reset input ( $MR$ ) is taken low.  $\overline{RST}$  is guaranteed to be a logic low (logic high for STM804/805) for  $0 \text{ V} < V_{CC} < V_{RST}$  if  $V_{BAT}$  is greater than 1 V. Without a backup battery,  $\overline{RST}$  is guaranteed valid down to  $V_{CC} = 1 \text{ V}$ .

During power-up, once  $V_{CC}$  exceeds the reset threshold an internal timer keeps  $\overline{RST}$  low for the reset time-out period,  $t_{rec}$ . After this interval  $\overline{RST}$  returns high.

If  $V_{CC}$  drops below the reset threshold,  $\overline{RST}$  goes low. Each time  $\overline{RST}$  is asserted, it stays low for at least the reset time-out period ( $t_{rec}$ ). Any time  $V_{CC}$  goes below the reset threshold the internal timer clears. The reset timer starts when  $V_{CC}$  returns above the reset threshold.

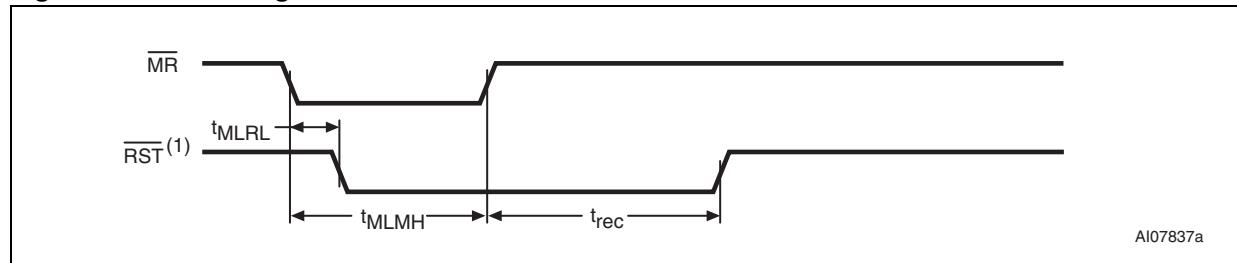

### 2.2 Push-button reset input (STM704/806)

A logic low on  $\overline{MR}$  asserts reset. Reset remains asserted while  $\overline{MR}$  is low, and for  $t_{rec}$  (see [Figure 36](#)) after it returns high. The  $\overline{MR}$  input has an internal  $40 \text{ k}\Omega$  pull-up resistor, allowing it to be left open if not used. This input can be driven with TTL/CMOS-logic levels or with open-drain/ collector outputs. Connect a normally open momentary switch from  $\overline{MR}$  to GND to create a manual reset function; external debounce circuitry is not required. If  $\overline{MR}$  is driven from long cables or the device is used in a noisy environment, connect a  $0.1\mu\text{F}$  capacitor from  $\overline{MR}$  to GND to provide additional noise immunity.  $\overline{MR}$  may float, or be tied to  $V_{CC}$  when not used.

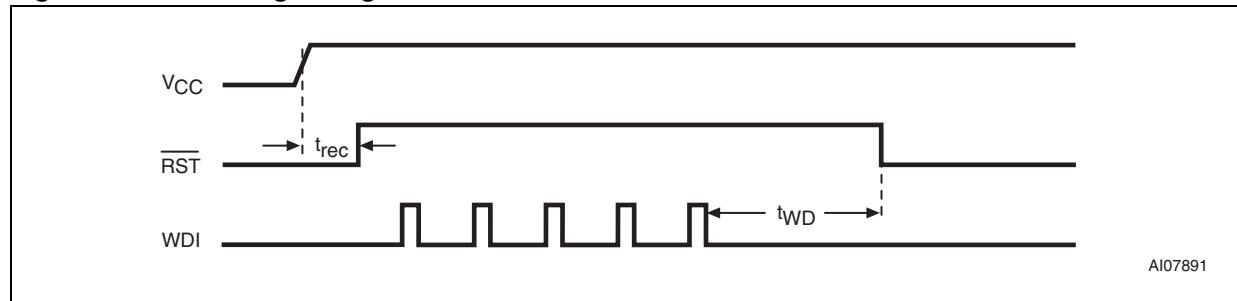

### 2.3 Watchdog input (NOT available on STM704/795/806)

The watchdog timer can be used to detect an out-of-control MCU. If the MCU does not toggle the watchdog input (WDI) within  $t_{WD}$  (1.6 s typ), the reset is asserted. The internal watchdog timer is cleared by either:

1. a reset pulse, or

2. by toggling WDI (high-to-low or low-to-high), which can detect pulses as short as 50 ns. If WDI is tied high or low, a reset pulse is triggered every 1.8 s ( $t_{WD} + t_{rec}$ ).

The timer remains cleared and does not count for as long as reset is asserted. As soon as reset is released, the timer starts counting (see [Figure 37](#)).

*Note:* *Input frequency greater than 20 ns (50 MHz) will be filtered.*

## 2.4 Backup battery switchover

In the event of a power failure, it may be necessary to preserve the contents of external SRAM through  $V_{OUT}$ . With a backup battery installed with voltage  $V_{BAT}$ , the devices automatically switch the SRAM to the backup supply when  $V_{CC}$  falls.

*Note:* *When the battery is first connected without  $V_{CC}$  power applied, the device does not immediately provide battery backup voltage on  $V_{OUT}$ . Only after  $V_{CC}$  exceeds  $V_{RST}$  will the switchover operate as described below. This mode allows a battery to be attached during manufacturing but not used until after the system has been activated for the first time. As a result, no battery power is consumed by the device during storage and shipment. If the backup battery is not used, connect both  $V_{BAT}$  and  $V_{OUT}$  to  $V_{CC}$ .*

This family of supervisors does not always connect  $V_{BAT}$  to  $V_{OUT}$  when  $V_{BAT}$  is greater than  $V_{CC}$ .  $V_{BAT}$  connects to  $V_{OUT}$  (through a  $100\ \Omega$  switch) when  $V_{CC}$  is below  $V_{SW}$  (2.4 V) or  $V_{BAT}$  (whichever is lower). This is done to allow the backup battery (e.g., a 3.6 V lithium cell) to have a higher voltage than  $V_{CC}$ .

Assuming that  $V_{BAT} > 2.0$  V, switchover at  $V_{SO}$  ensures that battery backup mode is entered before  $V_{OUT}$  gets too close to the 2.0 V minimum required to reliably retain data in most external SRAMs. When  $V_{CC}$  recovers, hysteresis is used to avoid oscillation around the  $V_{SO}$  point.  $V_{OUT}$  is connected to  $V_{CC}$  through a  $3\ \Omega$  PMOS power switch.

*Note:* *The backup battery may be removed while  $V_{CC}$  is valid, assuming  $V_{BAT}$  is adequately decoupled (0.1  $\mu$ F typ), without danger of triggering a reset.*

**Table 4. I/O status in battery backup**

| Pin                  | Status                                         |

|----------------------|------------------------------------------------|

| $V_{OUT}$            | Connected to $V_{BAT}$ through internal switch |

| $V_{CC}$             | Disconnected from $V_{OUT}$                    |

| PFI                  | Disabled                                       |

| $\overline{PFO}$     | Logic low                                      |

| $\overline{E}$       | High impedance                                 |

| $\overline{E}_{CON}$ | Logic high                                     |

| WDI                  | Watchdog timer is disabled                     |

| $\overline{MR}$      | Disabled                                       |

| $\overline{RST}$     | Logic low                                      |

| RST                  | Logic high                                     |

| $V_{BAT}$            | Connected to $V_{OUT}$                         |

| $V_{CCSW}$           | Logic high (STM795)                            |

## 2.5 Chip enable gating (STM795 only)

Internal gating of the chip enable ( $\bar{E}$ ) signal prevents erroneous data from corrupting the external CMOS RAM in the event of an undervoltage condition. The STM795 uses a series transmission gate from  $\bar{E}$  to  $\bar{E}_{CON}$  (see [Figure 11](#)). During normal operation (reset not asserted), the  $\bar{E}$  transmission gate is enabled and passes all  $\bar{E}$  transitions. When reset is asserted, this path becomes disabled, preventing erroneous data from corrupting the CMOS RAM. The short  $\bar{E}$  propagation delay from  $\bar{E}$  to  $\bar{E}_{CON}$  enables the STM795 to be used with most  $\mu$ Ps. If  $\bar{E}$  is low when reset asserts,  $\bar{E}_{CON}$  remains low for typically 10  $\mu$ s to permit the current write cycle to complete.

## 2.6 Chip enable input (STM795 only)

The chip enable transmission gate is disabled and  $\bar{E}$  is high impedance (disabled mode) while reset is asserted. During a power-down sequence when  $V_{CC}$  passes the reset threshold, the chip enable transmission gate disables and  $\bar{E}$  immediately becomes high impedance if the voltage at  $\bar{E}$  is high. If  $\bar{E}$  is low when reset asserts, the chip enable transmission gate will disable 10  $\mu$ s after reset asserts (see [Figure 12](#)). This permits the current write cycle to complete during power-down.

Any time a reset is generated, the chip enable transmission gate remains disabled and  $\bar{E}$  remains high impedance (regardless of  $\bar{E}$  activity) for the first half of the reset time-out period ( $t_{rec}/2$ ). When the chip enable transmission gate is enabled, the impedance of  $\bar{E}$  appears as a 40  $\Omega$  resistor in series with the load at  $\bar{E}_{CON}$ . The propagation delay through the chip enable transmission gate depends on  $V_{CC}$ , the source impedance of the drive connected to  $\bar{E}$ , and the loading on  $\bar{E}_{CON}$ . The chip enable propagation delay is production tested from the 50% point on  $\bar{E}$  to the 50% point on  $\bar{E}_{CON}$  using a 50  $\Omega$  driver and a 50 pF load capacitance (see [Figure 35](#)). For minimum propagation delay, minimize the capacitive load at  $\bar{E}_{CON}$  and use a low-output impedance driver.

## 2.7 Chip enable output (STM795 only)

When the chip enable transmission gate is enabled, the impedance of  $\bar{E}_{CON}$  is equivalent to a 40  $\Omega$  resistor in series with the source driving  $\bar{E}$ . In the disabled mode, the transmission gate is off and an active pull-up connects  $\bar{E}_{CON}$  to  $V_{OUT}$  (see [Figure 11](#)). This pull-up turns off when the transmission gate is enabled.

**Figure 11. Chip enable gating**

Figure 12. Chip enable waveform (STM795)

## 2.8 Power-fail input/output (NOT available on STM795)

The Power-Fail Input (PFI) is compared to an internal reference voltage (independent from the  $V_{RST}$  comparator). If PFI is less than the power-fail threshold ( $V_{PFI}$ ), the Power-Fail Output (PFO) will go low. This function is intended for use as an undervoltage detector to signal a failing power supply. Typically PFI is connected through an external voltage divider (see [Figure 10](#)) to either the unregulated DC input (if it is available) or the regulated output of the  $V_{CC}$  regulator. The voltage divider can be set up such that the voltage at PFI falls below  $V_{PFI}$  several milliseconds before the regulated  $V_{CC}$  input to the STM690/704/795/802/804/805/806 or the microprocessor drops below the minimum operating voltage.

During battery backup, the power-fail comparator is turned off and  $\overline{PFO}$  goes (or remains) low (see [Figure 13](#)). This occurs after  $V_{CC}$  drops below  $V_{SW}$  (2.4 V). When power returns, the power-fail comparator is enabled and  $\overline{PFO}$  follows PFI. If the comparator is unused, PFI should be connected to  $V_{SS}$  and  $\overline{PFO}$  left unconnected.  $\overline{PFO}$  may be connected to  $\overline{MR}$  on the STM704/806 so that a low voltage on PFI will generate a reset output.

## 2.9 Applications information

These supervisor circuits are not short-circuit protected. Shorting  $V_{OUT}$  to ground - excluding power-up transients such as charging a decoupling capacitor - destroys the device. Decouple both  $V_{CC}$  and  $V_{BAT}$  pins to ground by placing 0.1  $\mu$ F capacitors as close to the device as possible.

**Figure 13. Power-fail comparator waveform (STM690/704/802/804/805/806)**

## 2.10 Using a SuperCap™ as a backup power source

SuperCaps™ are capacitors with extremely high capacitance values (e.g., order of 0.47 F) for their size. [Figure 14](#) shows how to use a SuperCap as a backup power source. The SuperCap may be connected through a diode to the  $V_{CC}$  supply. Since  $V_{BAT}$  can exceed  $V_{CC}$  while  $V_{CC}$  is above the reset threshold, there are no special precautions when using these supervisors with a Super-Cap.

**Figure 14. Using a SuperCap™**

## 2.11 Negative-going $V_{CC}$ transients

The STM690/704/795/802/804/805/806 supervisors are relatively immune to negative-going  $V_{CC}$  transients (glitches). [Figure 32](#) was generated using a negative pulse applied to  $V_{CC}$ , starting at  $V_{RST} + 0.3$  V and ending below the reset threshold by the magnitude indicated (comparator overdrive). The graph indicates the maximum pulse width a negative  $V_{CC}$  transient can have without causing a reset pulse. As the magnitude of the transient increases (further below the threshold), the maximum allowable pulse width decreases. Any combination of duration and overdrive which lies under the curve will NOT generate a reset signal. Typically, a  $V_{CC}$  transient that goes 100 mV below the reset threshold and lasts 40  $\mu$ s or less will not cause a reset pulse. A 0.1  $\mu$ F bypass capacitor mounted as close as possible to the  $V_{CC}$  pin provides additional transient immunity.

### 3 Typical operating characteristics

Note: Typical values are at  $T_A = 25$  °C.

Figure 15.  $V_{CC}$  to  $V_{OUT}$  on-resistance vs. temperature

Figure 16.  $V_{BAT}$  to  $V_{OUT}$  on-resistance vs. temperature

Figure 17. Supply current vs. temperature (no load)

Figure 18. Battery current vs. temperature

Figure 19.  $V_{PFI}$  threshold vs. temperature

Figure 20. Reset comparator propagation delay vs. temperature

Figure 21. Power-up  $t_{rec}$  vs. temperature

Figure 22. Normalized reset threshold vs. temperature

Figure 23. Watchdog time-out period vs. temperature

Figure 24.  $\bar{E}$  to  $\bar{E}_{CON}$  on-resistance vs. temperature

Figure 25. PFI to PFO propagation delay vs. temperature

Figure 26. Output voltage vs. load current ( $V_{CC} = 5\text{ V}$ ;  $V_{BAT} = 2.8\text{ V}$ ;  $T_A = 25\text{ °C}$ )

Figure 27. Output voltage vs. load current ( $V_{CC} = 0 \text{ V}$ ;  $V_{BAT} = 2.8 \text{ V}$ ;  $T_A = 25 \text{ }^\circ\text{C}$ )

Figure 28. RST output voltage vs. supply voltage

Figure 29. RST output voltage vs. supply voltage

Figure 30. Power-fail comparator response time (assertion)

Figure 31. Power-fail comparator response time (de-assertion)

Figure 32. Maximum transient duration vs. reset threshold overdrive

Figure 33.  $\bar{E}$  to  $\bar{E}_{CON}$  propagation delay vs. temperature

## 4 Maximum ratings

Stressing the device above the rating listed in the absolute maximum ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 5. Absolute maximum ratings**

| Symbol           | Parameter                              | Value                 | Unit |

|------------------|----------------------------------------|-----------------------|------|

| $T_{STG}$        | Storage temperature ( $V_{CC}$ off)    | –55 to 150            | °C   |

| $T_{SLD}^{(1)}$  | Lead solder temperature for 10 seconds | 260                   | °C   |

| $V_{IO}$         | Input or output voltage                | –0.3 to $V_{CC}$ +0.3 | V    |

| $V_{CC}/V_{BAT}$ | Supply voltage                         | –0.3 to 6.0           | V    |

| $I_O$            | Output current                         | 20                    | mA   |

| $P_D$            | Power dissipation                      | 320                   | mW   |

1. Reflow at peak temperature of 260 °C. The time above 255 °C must not exceed 30 seconds.

## 5 DC and AC parameters

This section summarizes the operating measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC characteristics tables that follow, are derived tests performed under the measurement conditions summarized in [Table 6](#). Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

**Table 6. Operating and AC measurement conditions**

| Parameter                               | STM690/704/795/<br>802/804/805/806 | Unit |

|-----------------------------------------|------------------------------------|------|

| $V_{CC}/V_{BAT}$ supply voltage         | 1.0 to 5.5                         | V    |

| Ambient operating temperature ( $T_A$ ) | -40 to 85                          | °C   |

| Input rise and fall times               | $\leq 5$                           | ns   |

| Input pulse voltages                    | 0.2 to 0.8 $V_{CC}$                | V    |

| Input and output timing ref. voltages   | 0.3 to 0.7 $V_{CC}$                | V    |

**Figure 34.  $\bar{E}$  to  $\bar{E}_{CON}$  propagation delay test circuit**

1.  $C_L$  includes load capacitance and scope probe capacitance.

**Figure 35. AC testing input/output waveforms**

Figure 36.  $\overline{\text{MR}}$  timing waveform

1. RST for STM805.

Figure 37. Watchdog timing

Table 7. DC and AC characteristics

| Sym                     | Alter-native | Description                                     | Test condition <sup>(1)</sup>                                                                | Min                | Typ               | Max | Unit     |

|-------------------------|--------------|-------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|-------------------|-----|----------|

| $V_{CC}, V_{BAT}^{(2)}$ |              | Operating voltage                               | $T_A = -40$ to $+85$ °C                                                                      | 1.1 <sup>(3)</sup> |                   | 5.5 | V        |

| $I_{CC}$                |              | $V_{CC}$ supply current                         | Excluding $I_{OUT}$ ( $V_{CC} < 5.5$ V)                                                      |                    | 40                | 60  | $\mu$ A  |

|                         |              |                                                 | Excluding $I_{OUT}$ ( $V_{CC} < 3.6$ V)                                                      |                    | 35                | 50  | $\mu$ A  |

|                         |              | $V_{CC}$ supply current in battery backup mode  | Excluding $I_{OUT}$ ( $V_{BAT} = 2.3$ V, $V_{CC} = 2.0$ V, $\overline{\text{MR}} = V_{CC}$ ) |                    | 25                | 35  | $\mu$ A  |

| $I_{BAT}^{(4)}$         |              | $V_{BAT}$ supply current in battery backup mode | Excluding $I_{OUT}$ ( $V_{BAT} = 3.6$ V)                                                     |                    | 0.4               | 1.0 | $\mu$ A  |

| $V_{OUT1}$              |              | $V_{OUT}$ voltage (active)                      | $I_{OUT1} = 5$ mA <sup>(5)</sup>                                                             | $V_{CC} - 0.03$    | $V_{CC} - 0.015$  |     | V        |

|                         |              |                                                 | $I_{OUT1} = 75$ mA                                                                           | $V_{CC} - 0.3$     | $V_{CC} - 0.15$   |     | V        |

|                         |              |                                                 | $I_{OUT1} = 250$ $\mu$ A, $V_{CC} > 2.5$ V <sup>(5)</sup>                                    | $V_{CC} - 0.0015$  | $V_{CC} - 0.0006$ |     | V        |

| $V_{OUT2}$              |              | $V_{OUT}$ voltage (battery backup)              | $I_{OUT2} = 250$ $\mu$ A, $V_{BAT} = 2.3$ V                                                  | $V_{BAT} - 0.1$    | $V_{BAT} - 0.034$ |     | V        |

|                         |              |                                                 | $I_{OUT2} = 1$ mA, $V_{BAT} = 2.3$ V                                                         |                    | $V_{BAT} - 0.14$  |     | V        |

|                         |              | $V_{CC}$ to $V_{OUT}$ on-resistance             |                                                                                              |                    | 3                 | 4   | $\Omega$ |

Table 7. DC and AC characteristics (continued)

| Sym                                                    | Alter-native | Description                                                                          | Test condition <sup>(1)</sup>                                                             | Min                | Typ   | Max          | Unit     |   |

|--------------------------------------------------------|--------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|-------|--------------|----------|---|

|                                                        |              | $V_{BAT}$ to $V_{OUT}$ on-resistance                                                 |                                                                                           |                    | 100   |              | $\Omega$ |   |

| $I_{LI}$                                               |              | Input leakage current ( $\overline{MR}$ )                                            | STM704/806 only;<br>$\overline{MR} = 0$ V, $V_{CC} = 3$ V                                 | 20                 | 75    | 350          | $\mu$ A  |   |

|                                                        |              | Input leakage current (PFI)                                                          | $0$ V < $V_{IN}$ < $V_{CC}$                                                               | -20                | 2     | +25          | nA       |   |

|                                                        |              | Input leakage current (WDI)                                                          | $0$ V < $V_{IN}$ < $V_{CC}$                                                               | -1                 |       | +1           | $\mu$ A  |   |

| $I_{LO}$                                               |              | Output leakage current                                                               | STM804/805/795;<br>$0$ V < $V_{IN}$ < $V_{CC}$ <sup>(6)</sup>                             | -1                 |       | +1           | $\mu$ A  |   |

| $V_{IH}$                                               |              | Input high voltage ( $\overline{MR}$ , WDI)                                          | $V_{RST}$ (max) < $V_{CC}$ < 5.5 V                                                        | 0.7 $V_{CC}$       |       |              | V        |   |

| $V_{IL}$                                               |              | Input low voltage ( $\overline{MR}$ , WDI)                                           | $V_{RST}$ (max) < $V_{CC}$ < 5.5 V                                                        |                    |       | 0.3 $V_{CC}$ | V        |   |

| $V_{OL}$                                               |              | Output low voltage ( $\overline{PFO}$ , $\overline{RST}$ , RST, $\overline{Vccsw}$ ) | $V_{CC} = V_{RST}$ (max),<br>$I_{SINK} = 3.2$ mA                                          |                    |       | 0.3          | V        |   |

|                                                        |              | Output low voltage ( $\overline{E}_{CON}$ )                                          | $V_{CC} = V_{RST}$ (max),<br>$I_{OUT} = 1.6$ mA, $E = 0$ V                                |                    |       | 0.2 $V_{CC}$ | V        |   |

| $V_{OL}$                                               |              | Output low voltage ( $\overline{RST}$ )                                              | $I_{OL} = 40$ $\mu$ A,<br>$V_{CC} = 1.0$ V, $V_{BAT} = V_{CC}$ ,<br>$T_A = 0$ °C to 85 °C |                    |       | 0.3          | V        |   |

|                                                        |              |                                                                                      | $I_{OL} = 200$ $\mu$ A,<br>$V_{CC} = 1.2$ V, $V_{BAT} = V_{CC}$                           |                    |       | 0.3          | V        |   |

| $V_{OH}$                                               |              | Output high voltage ( $\overline{RST}$ , RST) <sup>(7)</sup>                         | $I_{SOURCE} = 1$ mA,<br>$V_{CC} = V_{RST}$ (max)                                          | 2.4                |       |              | V        |   |

|                                                        |              | Output high voltage ( $\overline{E}_{CON}$ )                                         | $V_{CC} = V_{RST}$ (max),<br>$I_{OUT} = 1.6$ mA, $\overline{E} = V_{CC}$                  | 0.8 $V_{CC}$       |       |              | V        |   |

|                                                        |              | Output high voltage ( $\overline{PFO}$ )                                             | $I_{SOURCE} = 75$ $\mu$ A,<br>$V_{CC} = V_{RST}$ (max)                                    | 0.8 $V_{CC}$       |       |              | V        |   |

| $V_{OHB}$                                              |              | $V_{OH}$ battery backup ( $\overline{Vccsw}$ , RST)                                  | $I_{SOURCE} = 100$ $\mu$ A,<br>$V_{CC} = 0$ V, $V_{BAT} = 2.8$ V                          | 0.8 $V_{BAT}$      |       |              | V        |   |

|                                                        |              | $V_{OH}$ battery backup ( $\overline{E}_{CON}$ )                                     | $I_{SOURCE} = 75$ $\mu$ A,<br>$V_{CC} = 0$ V, $V_{BAT} = 2.8$ V                           | 0.8 $V_{BAT}$      |       |              | V        |   |

| <b>Power-fail comparator (NOT available on STM795)</b> |              |                                                                                      |                                                                                           |                    |       |              |          |   |

| $V_{PFI}$                                              |              | PFI input threshold                                                                  | PFI falling<br>( $V_{CC} < 3.6$ V)                                                        | STM802/<br>804/806 | 1.212 | 1.237        | 1.262    | V |

|                                                        |              |                                                                                      |                                                                                           | STM690/<br>704/805 | 1.187 | 1.237        | 1.287    | V |

|                                                        |              | PFI hysteresis                                                                       | PFI rising ( $V_{CC} < 3.6$ V)                                                            |                    | 10    | 20           | mV       |   |

| $t_{PFD}$                                              |              | PFI to $\overline{PFO}$ propagation delay                                            |                                                                                           |                    | 2     |              | $\mu$ s  |   |

Table 7. DC and AC characteristics (continued)

| Sym                                                     | Alter-native     | Description                                         | Test condition <sup>(1)</sup>                    | Min                                | Typ  | Max              | Unit |   |

|---------------------------------------------------------|------------------|-----------------------------------------------------|--------------------------------------------------|------------------------------------|------|------------------|------|---|

| I <sub>SC</sub>                                         |                  | PFO output short to GND current                     | V <sub>CC</sub> = 3.6 V, PFO = 0 V               | 0.1                                | 0.75 | 2.0              | mA   |   |

| <b>Battery switchover</b>                               |                  |                                                     |                                                  |                                    |      |                  |      |   |

| V <sub>SO</sub>                                         |                  | Battery backup switchover voltage <sup>(8)(9)</sup> | Power-down                                       | V <sub>BAT</sub> > V <sub>SW</sub> |      | V <sub>SW</sub>  | V    |   |

|                                                         |                  |                                                     |                                                  | V <sub>BAT</sub> < V <sub>SW</sub> |      | V <sub>BAT</sub> | V    |   |

|                                                         |                  |                                                     | Power-up                                         | V <sub>BAT</sub> > V <sub>SW</sub> |      | V <sub>SW</sub>  | V    |   |

|                                                         |                  |                                                     |                                                  | V <sub>BAT</sub> < V <sub>SW</sub> |      | V <sub>BAT</sub> | V    |   |

|                                                         |                  | V <sub>SW</sub>                                     |                                                  |                                    | 2.4  |                  | V    |   |

|                                                         |                  | Hysteresis                                          |                                                  |                                    | 40   |                  | mV   |   |

| <b>Reset thresholds</b>                                 |                  |                                                     |                                                  |                                    |      |                  |      |   |

| V <sub>RST</sub> <sup>(10)</sup>                        |                  | Reset threshold                                     | STM690T/704T/795T/ 805T                          | V <sub>CC</sub> falling            | 3.00 | 3.075            | 3.15 | V |

|                                                         |                  |                                                     |                                                  | V <sub>CC</sub> rising             | 3.00 | 3.085            | 3.17 | V |

|                                                         |                  |                                                     | STM802T/804T/806T                                | V <sub>CC</sub> falling            | 3.00 | 3.075            | 3.12 | V |

|                                                         |                  |                                                     |                                                  | V <sub>CC</sub> rising             | 3.00 | 3.085            | 3.14 | V |

|                                                         |                  |                                                     | STM690S/704S/795S/ 805S                          | V <sub>CC</sub> falling            | 2.85 | 2.925            | 3.00 | V |

|                                                         |                  |                                                     |                                                  | V <sub>CC</sub> rising             | 2.85 | 2.935            | 3.02 | V |

|                                                         |                  |                                                     | STM802S/804S/806S                                | V <sub>CC</sub> falling            | 2.88 | 2.925            | 3.00 | V |

|                                                         |                  |                                                     |                                                  | V <sub>CC</sub> rising             | 2.88 | 2.935            | 3.02 | V |

|                                                         |                  |                                                     | STM690R/704R/795R/ 805R                          | V <sub>CC</sub> falling            | 2.55 | 2.625            | 2.70 | V |

|                                                         |                  |                                                     |                                                  | V <sub>CC</sub> rising             | 2.55 | 2.635            | 2.72 | V |

|                                                         |                  |                                                     | STM802R/804R/806R                                | V <sub>CC</sub> falling            | 2.59 | 2.625            | 2.70 | V |

|                                                         |                  |                                                     |                                                  | V <sub>CC</sub> rising             | 2.59 | 2.635            | 2.72 | V |

| t <sub>rec</sub>                                        |                  | RST pulse width                                     | V <sub>CC</sub> < 3.6 V                          | 140                                | 200  | 280              | ms   |   |

| <b>Push-button reset input (STM704/806)</b>             |                  |                                                     |                                                  |                                    |      |                  |      |   |

| t <sub>MLMH</sub>                                       | t <sub>MR</sub>  | MR pulse width                                      |                                                  | 100                                | 20   |                  | ns   |   |

| t <sub>MLRL</sub>                                       | t <sub>MRD</sub> | MR to RST output delay                              |                                                  |                                    | 60   | 500              | ns   |   |

| <b>Watchdog timer (NOT available on STM704/795/806)</b> |                  |                                                     |                                                  |                                    |      |                  |      |   |

| t <sub>WD</sub>                                         |                  | Watchdog timeout period                             | V <sub>RST</sub> (max) < V <sub>CC</sub> < 3.6 V | 1.12                               | 1.60 | 2.24             | s    |   |

|                                                         |                  | WDI pulse width                                     | V <sub>RST</sub> (max) < V <sub>CC</sub> < 3.6 V | 100                                | 20   |                  | ns   |   |

| <b>Chip enable gating (STM795 only)</b>                 |                  |                                                     |                                                  |                                    |      |                  |      |   |

|                                                         |                  | E to E <sub>CON</sub> resistance                    | V <sub>CC</sub> = V <sub>RST</sub> (max)         |                                    | 46   |                  | Ω    |   |

**Table 7. DC and AC characteristics (continued)**

| Sym      | Alter-native | Description                                    | Test condition <sup>(1)</sup>                            | Min | Typ  | Max | Unit    |

|----------|--------------|------------------------------------------------|----------------------------------------------------------|-----|------|-----|---------|

|          |              | $\bar{E}$ to $\bar{E}_{CON}$ propagation delay | $V_{CC} = V_{RST}$ (max)                                 |     | 2    | 7   | ns      |

|          |              | Reset to $\bar{E}_{CON}$ high delay            |                                                          |     | 10   |     | $\mu$ s |

| $I_{SC}$ |              | $\bar{E}_{CON}$ short circuit current          | $V_{CC} = 3.6$ V, disable mode,<br>$\bar{E}_{CON} = 0$ V | 0.1 | 0.75 | 2.0 | mA      |

1. Valid for ambient operating temperature:  $T_A = -40$  to  $85$  °C;  $V_{CC} = V_{RST}$  (max) to  $5.5$  V; and  $V_{BAT} = 2.8$  V (except where noted).

2.  $V_{CC}$  supply current, logic input leakage, watchdog functionality, push-button reset functionality, PFI functionality, state of RST and RST tested at  $V_{BAT} = 3.6$  V, and  $V_{CC} = 5.5$  V. The state of RST or RST and PFO is tested at  $V_{CC} = V_{CC}$  (min). Either  $V_{CC}$  or  $V_{BAT}$  can go to 0 V if the other is greater than 2.0 V.

3.  $V_{CC}$  (min) = 1.0 V for  $T_A = 0$  °C to +85 °C.

4. Tested at  $V_{BAT} = 3.6$  V,  $V_{CC} = 3.5$  V and 0 V.

5. Guaranteed by design.

6. The leakage current measured on the RST pin (STM804/805) or  $\bar{RST}$  pin (STM795) is tested with the reset output not asserted (output high impedance).

7. Not valid for STM795/804/805 (open drain).

8. When  $V_{BAT} > V_{CC} > V_{SW}$ ,  $V_{OUT}$  remains connected to  $V_{CC}$  until  $V_{CC}$  drops below  $V_{SW}$ .

9. When  $V_{SW} > V_{CC} > V_{BAT}$ ,  $V_{OUT}$  remains connected to  $V_{CC}$  until  $V_{CC}$  drops below the battery voltage ( $V_{BAT}$ ) - 75 mV.

10. The reset threshold tolerance is wider for  $V_{CC}$  rising than for  $V_{CC}$  falling due to the 10 mV (typ) hysteresis, which prevents internal oscillation.

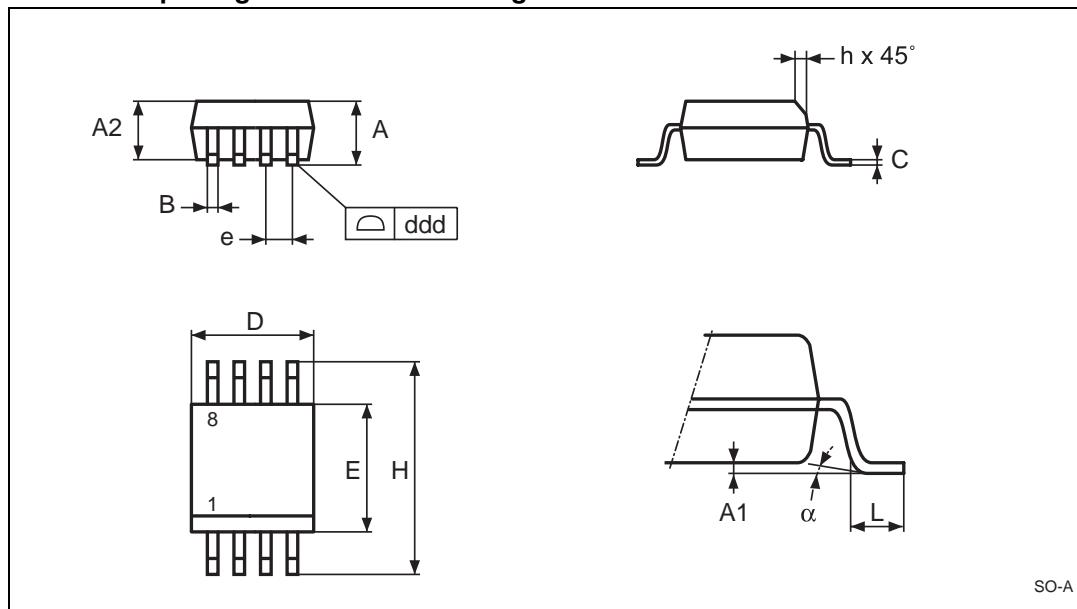

## 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: [www.st.com](http://www.st.com).

ECOPACK® is an ST trademark.

**Figure 38. SO8 – 8-lead plastic small outline, 150 mils body width, package mechanical drawing**

**Table 8. SO8 - 8-lead plastic small outline, 150 mils body width, package mechanical data**

| Symb | mm   |      |      | inches |       |       |

|------|------|------|------|--------|-------|-------|

|      | Typ  | Min  | Max  | Typ    | Min   | Max   |

| A    | —    | 1.35 | 1.75 | —      | 0.053 | 0.069 |

| A1   | —    | 0.10 | 0.25 | —      | 0.004 | 0.010 |

| B    | —    | 0.33 | 0.51 | —      | 0.013 | 0.020 |

| C    | —    | 0.19 | 0.25 | —      | 0.007 | 0.010 |

| D    | —    | 4.80 | 5.00 | —      | 0.189 | 0.197 |

| ddd  | —    | —    | 0.10 | —      | —     | 0.004 |

| E    | —    | 3.80 | 4.00 | —      | 0.150 | 0.157 |

| e    | 1.27 | —    | —    | 0.050  | —     | —     |

| H    | —    | 5.80 | 6.20 | —      | 0.228 | 0.244 |

| h    | —    | 0.25 | 0.50 | —      | 0.010 | 0.020 |

| L    | —    | 0.40 | 0.90 | —      | 0.016 | 0.035 |

| α    | —    | 0°   | 8°   | —      | 0°    | 8°    |

| N    | 8    |      |      | 8      |       |       |

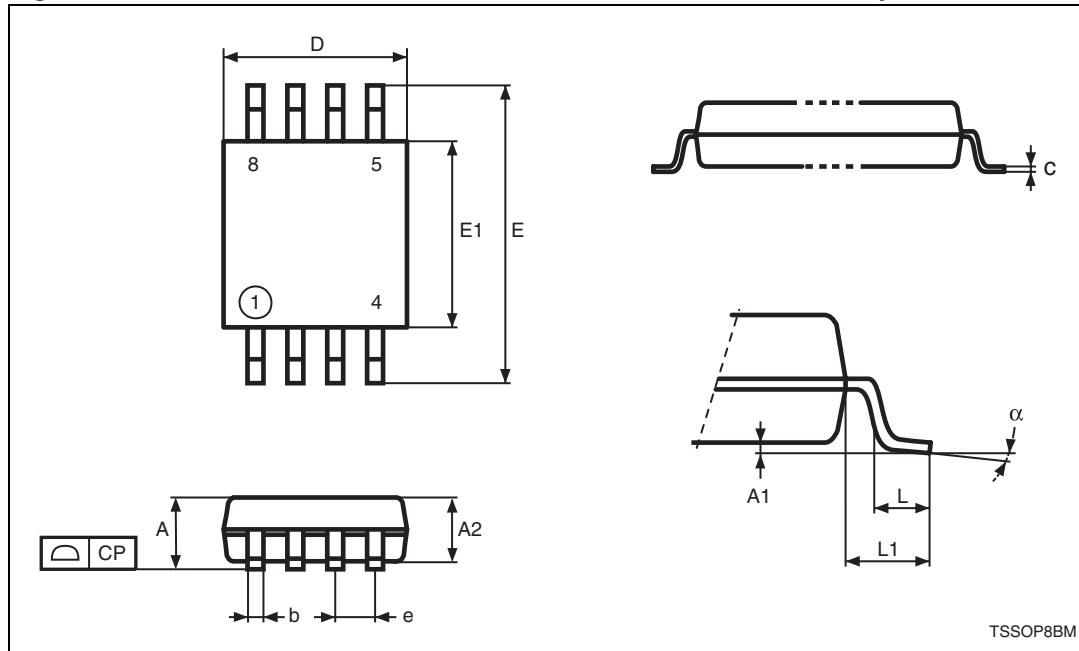

Figure 39. TSSOP8 – 8-lead, thin shrink small outline, 3 x 3 mm body size, outline

Table 9. TSSOP8 - 8-lead, thin shrink small outline, 3 x 3 mm body size, mechanical data

| Symb     | mm   |           |           | inches |           |           |

|----------|------|-----------|-----------|--------|-----------|-----------|

|          | Typ  | Min       | Max       | Typ    | Min       | Max       |

| A        | —    | —         | 1.10      | —      | —         | 0.043     |

| A1       | —    | 0.05      | 0.15      | —      | 0.002     | 0.006     |

| A2       | 0.85 | 0.75      | 0.95      | 0.034  | 0.030     | 0.037     |

| b        | —    | 0.25      | 0.40      | —      | 0.010     | 0.016     |

| c        | —    | 0.13      | 0.23      | —      | 0.005     | 0.009     |

| CP       | —    | —         | 0.10      | —      | —         | 0.004     |

| D        | 3.00 | 2.90      | 3.10      | 0.118  | 0.114     | 0.122     |

| e        | 0.65 | —         | —         | 0.026  | —         | —         |

| E        | 4.90 | 4.65      | 5.15      | 0.193  | 0.183     | 0.203     |

| E1       | 3.00 | 2.90      | 3.10      | 0.118  | 0.114     | 0.122     |

| L        | 0.55 | 0.40      | 0.70      | 0.022  | 0.016     | 0.030     |

| L1       | 0.95 | —         | —         | 0.037  | —         | —         |

| $\alpha$ | —    | $0^\circ$ | $6^\circ$ | —      | $0^\circ$ | $6^\circ$ |

| N        | 8    | 8         |           |        |           |           |

## 7 Part numbering

**Table 10. Ordering information scheme**

| Example:                                              | STM690 | T | M | 6 | E |

|-------------------------------------------------------|--------|---|---|---|---|

| <b>Device type</b>                                    |        |   |   |   |   |

| STM690/704/795/802/804/805/806                        |        |   |   |   |   |

| <b>Reset threshold voltage</b>                        |        |   |   |   |   |

| T = STM690/704/795/805 = $V_{RST}$ = 3.00 V to 3.15 V |        |   |   |   |   |

| STM802/804/806 = $V_{RST}$ = 3.00 V to 3.12 V         |        |   |   |   |   |

| S = STM690/704/795/805 = $V_{RST}$ = 2.85 V to 3.00 V |        |   |   |   |   |

| STM802/804/806 = $V_{RST}$ = 2.88 V to 3.00 V         |        |   |   |   |   |

| R = STM690/704/795/805 = $V_{RST}$ = 2.55 V to 2.70 V |        |   |   |   |   |

| STM802/804/806 = $V_{RST}$ = 2.59 V to 2.70 V         |        |   |   |   |   |

| <b>Package</b>                                        |        |   |   |   |   |

| M = SO8                                               |        |   |   |   |   |

| DS <sup>(1)</sup> = TSSOP8                            |        |   |   |   |   |

| <b>Temperature range</b>                              |        |   |   |   |   |

| 6 = -40 to 85 °C                                      |        |   |   |   |   |

| <b>Shipping method</b>                                |        |   |   |   |   |

| E = ECOPACK® package, tubes                           |        |   |   |   |   |

| F = ECOPACK® package, tape and reel                   |        |   |   |   |   |

1. Contact local ST sales office for availability.

For other options, or for more information on any aspect of this device, please contact the ST sales office nearest you.

Table 11. Marking description

| Part number | Reset threshold | Package | Topside marking |

|-------------|-----------------|---------|-----------------|

| STM690T     | 3.075           | SO8     | 690T            |

|             |                 | TSSOP8  |                 |

| STM690S     | 2.925           | SO8     | 690S            |

|             |                 | TSSOP8  |                 |

| STM690R     | 2.625           | SO8     | 690R            |

|             |                 | TSSOP8  |                 |

| STM704T     | 3.075           | SO8     | 704T            |

|             |                 | TSSOP8  |                 |

| STM704S     | 2.925           | SO8     | 704S            |

|             |                 | TSSOP8  |                 |

| STM704R     | 2.625           | SO8     | 704R            |

|             |                 | TSSOP8  |                 |

| STM795T     | 3.075           | SO8     | 795T            |

|             |                 | TSSOP8  |                 |

| STM795S     | 2.925           | SO8     | 795S            |

|             |                 | TSSOP8  |                 |

| STM795R     | 2.625           | SO8     | 795R            |

|             |                 | TSSOP8  |                 |

| STM802T     | 3.075           | SO8     | 802T            |

|             |                 | TSSOP8  |                 |

| STM802S     | 2.925           | SO8     | 802S            |

|             |                 | TSSOP8  |                 |

| STM802R     | 2.625           | SO8     | 802R            |

|             |                 | TSSOP8  |                 |

| STM804T     | 3.075           | SO8     | 804T            |

|             |                 | TSSOP8  |                 |

| STM804S     | 2.925           | SO8     | 804S            |

|             |                 | TSSOP8  |                 |

| STM804R     | 2.625           | SO8     | 804R            |

|             |                 | TSSOP8  |                 |

| STM805T     | 3.075           | SO8     | 805T            |

|             |                 | TSSOP8  |                 |

| STM805S     | 2.925           | SO8     | 805S            |

|             |                 | TSSOP8  |                 |

| STM805R     | 2.625           | SO8     | 805R            |

|             |                 | TSSOP8  |                 |

| STM806T     | 3.075           | SO8     | 806T            |

|             |                 | TSSOP8  |                 |

| STM806S     | 2.925           | SO8     | 806S            |

|             |                 | TSSOP8  |                 |

| STM806R     | 2.625           | SO8     | 806R            |

|             |                 | TSSOP8  |                 |

## 8 Revision history

**Table 12. Document revision history**

| Date        | Revision | Changes                                                                                                                                    |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 31-Oct-2003 | 1        | Initial release.                                                                                                                           |

| 22-Dec-2003 | 2        | Reformatted; update characteristics ( <a href="#">Figure 1, 3, 4, 11, 13, 14, 37</a> ; <a href="#">Table 1, 3, 4, 7, 9, 11</a> ).          |

| 16-Jan-2004 | 2.1      | Added <i>Typical operating characteristics</i> ( <a href="#">Figure 17, 18, 20 to 26, 29, 30 to 34</a> ).                                  |

| 07-Apr-2004 | 2.2      | Updated characteristics ( <a href="#">Figure 13, 29, 30, Table 1, 3, 7</a> )                                                               |

| 25-May-2004 | 3        | Update characteristics ( <a href="#">Table 3, 7</a> )                                                                                      |

| 02-Jul-2004 | 4        | Update package availability, pin description; promote document ( <a href="#">Figure 1, 14; Table 3, 10</a> )                               |

| 29-Sep-2004 | 5        | Clarify root part numbers, pin descriptions, update characteristics ( <a href="#">Figure 2, to, 11, 13, 14, 35; Table 1, 3, 6, 7, 10</a> ) |

| 25-Feb-2005 | 6        | Update characteristics ( <a href="#">Figure 11, 16, to 35; Table 7</a> )                                                                   |

| 05-Apr-2006 | 7        | Update characteristics ( <a href="#">Figure 13</a> )                                                                                       |

| 20-Nov-2009 | 8        | Updated <a href="#">Section 1.1.6, Section 1.1.8, Figure 10, 11, 19, Table 3, 5, 7</a> ; added text to <a href="#">Section 6</a> .         |

| 18-Aug-2010 | 9        | Updated <a href="#">Features, Section 2.4: Backup battery switchover</a> .                                                                 |

**Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

**UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.**

**UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.**

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

[www.st.com](http://www.st.com)

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## STMicroelectronics:

[STM802TM6F](#) [STM805TM6F](#) [STM804TM6F](#) [STM690SM6F](#) [STM795TM6F](#) [STM704TM6F](#) [STM704SM6F](#)

[STM802SM6F](#) [STM802RM6F](#) [STM804SM6F](#) [STM806TM6F](#) [STM805RM6F](#) [STM795RM6F](#) [STM795SM6F](#)

[STM690RM6F](#) [STM806SM6F](#) [STM804RM6F](#) [STM806RM6F](#) [STM690TM6F](#) [STM805SM6F](#) [STM704SDS6F](#)