## LM7600x-Q1 3.5-V to 60-V, 2.5-A/3.5-A Synchronous Step-Down Voltage Regulator

### 1 Features

- AEC-Q100 qualified for automotive applications

- Device temperature grade 1:  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  ambient operating temperature

- Device HBM ESD classification level 2

- Device CDM ESD classification level C5

- Integrated synchronous rectification

- Input voltage 3.5 V to 60 V (65 V maximum)

- Output voltage 1 V to 95%  $V_{\text{IN}}$

- 15- $\mu\text{A}$  Quiescent current in regulation

- Wide voltage conversion range

- $t_{\text{ON-MIN}} = 65 \text{ ns}$  (typical)

- $t_{\text{OFF-MIN}} = 95 \text{ ns}$  (typical)

- System-level features

- Synchronization to external clock

- Power-good flag

- Adjustable soft-start (6.3 ms default)

- Pin-selectable FPWM operation

- Adjustable frequency range: 300 kHz to 2.2 MHz

- High-efficiency at light-load architecture (PFM)

- Protection features

- Cycle-by-cycle current limit

- Short-circuit protection with hiccup mode

- Overtemperature thermal shutdown protection

- Create a custom design using the LM76002-Q1/LM76003-Q1 with the [WEBENCH® Power Designer](#)

### 2 Applications

- Camera applications for commercial vehicles

- Infotainment and cluster

- Hybrid electric vehicles

- Electric vehicles

### 3 Description

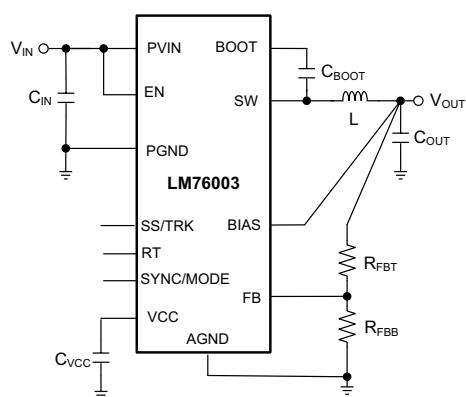

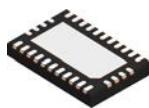

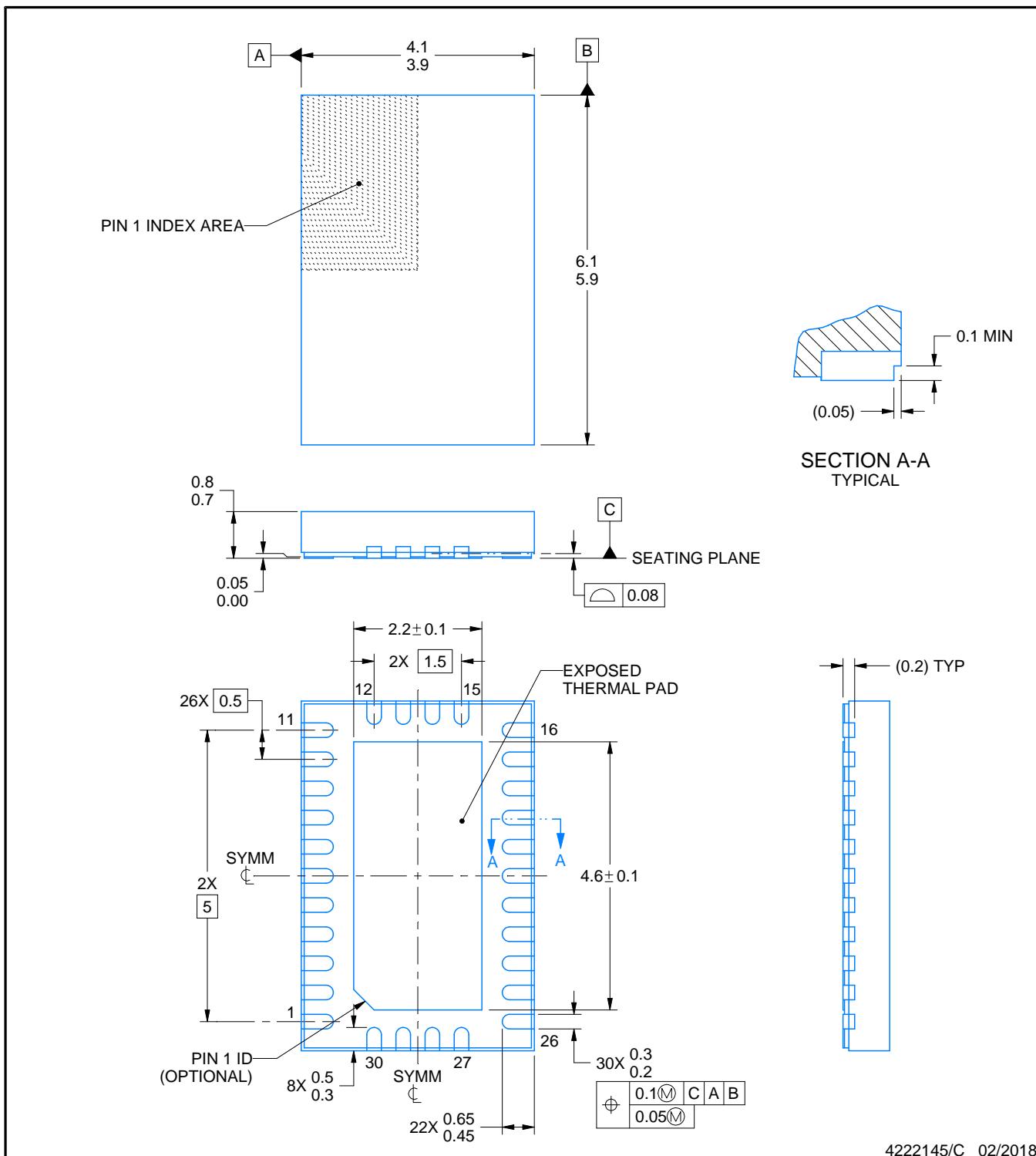

The LM76002-Q1/LM76003-Q1 regulator is an easy-to-use synchronous step-down DC-DC converter capable of driving up to 2.5 A (LM76002-Q1) or 3.5 A (LM76003-Q1) of load current from an input up to 60 V. The LM76002-Q1/LM76003-Q1 provides exceptional efficiency and output accuracy in a very small solution size. Peak current-mode control is employed. Additional features such as adjustable switching frequency, synchronization, FPWM option, power-good flag, precision enable, adjustable soft start, and tracking provide both flexible and easy-to-use solutions for a wide range of applications. Automatic frequency foldback at light load and optional external bias improve efficiency. This device requires few external components and has a pinout designed for simple PCB layout with best-in-class EMI (CISPR25) and thermal performance. Protection features include input undervoltage lockout, thermal shutdown, cycle-by-cycle current limit, and short-circuit protection. The LM76002-Q1/LM76003-Q1 device is available in the WQFN 30-pin leadless package with wettable flanks.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LM76002-Q1  | WQFN (30) | 6.00 mm x 4.00 mm |

| LM76003-Q1  |           |                   |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

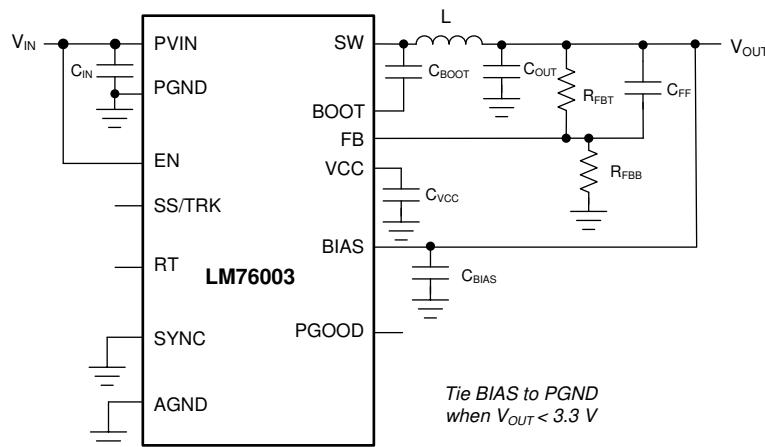

### Simplified Schematic

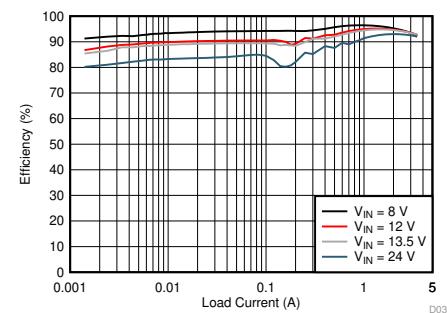

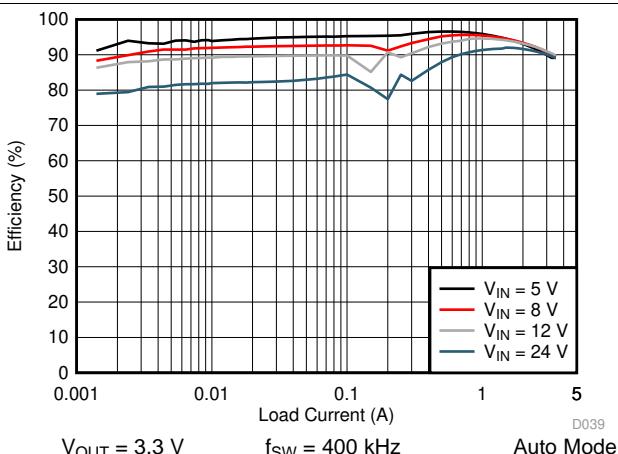

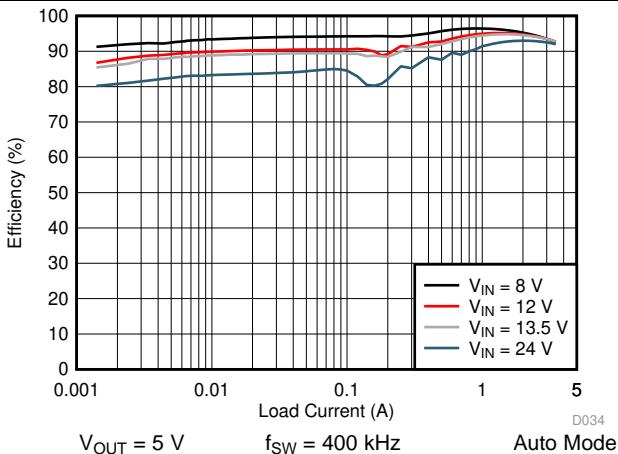

### Efficiency vs Output Current ( $V_{\text{OUT}} = 5 \text{ V}$ , $f_{\text{sw}} = 400 \text{ kHz}$ , Auto Mode)

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|          |                                        |    |           |                                                         |    |

|----------|----------------------------------------|----|-----------|---------------------------------------------------------|----|

| <b>1</b> | <b>Features</b>                        | 1  | 7.3       | Feature Description                                     | 13 |

| <b>2</b> | <b>Applications</b>                    | 1  | 7.4       | Device Functional Modes                                 | 22 |

| <b>3</b> | <b>Description</b>                     | 1  | <b>8</b>  | <b>Application and Implementation</b>                   | 24 |

| <b>4</b> | <b>Revision History</b>                | 2  | 8.1       | Application Information                                 | 24 |

| <b>5</b> | <b>Pin Configuration and Functions</b> | 3  | 8.2       | Typical Applications                                    | 24 |

| <b>6</b> | <b>Specifications</b>                  | 5  | <b>9</b>  | <b>Power Supply Recommendations</b>                     | 42 |

| 6.1      | Absolute Maximum Ratings               | 5  | <b>10</b> | <b>Layout</b>                                           | 42 |

| 6.2      | ESD Ratings                            | 5  | 10.1      | Layout Guidelines                                       | 42 |

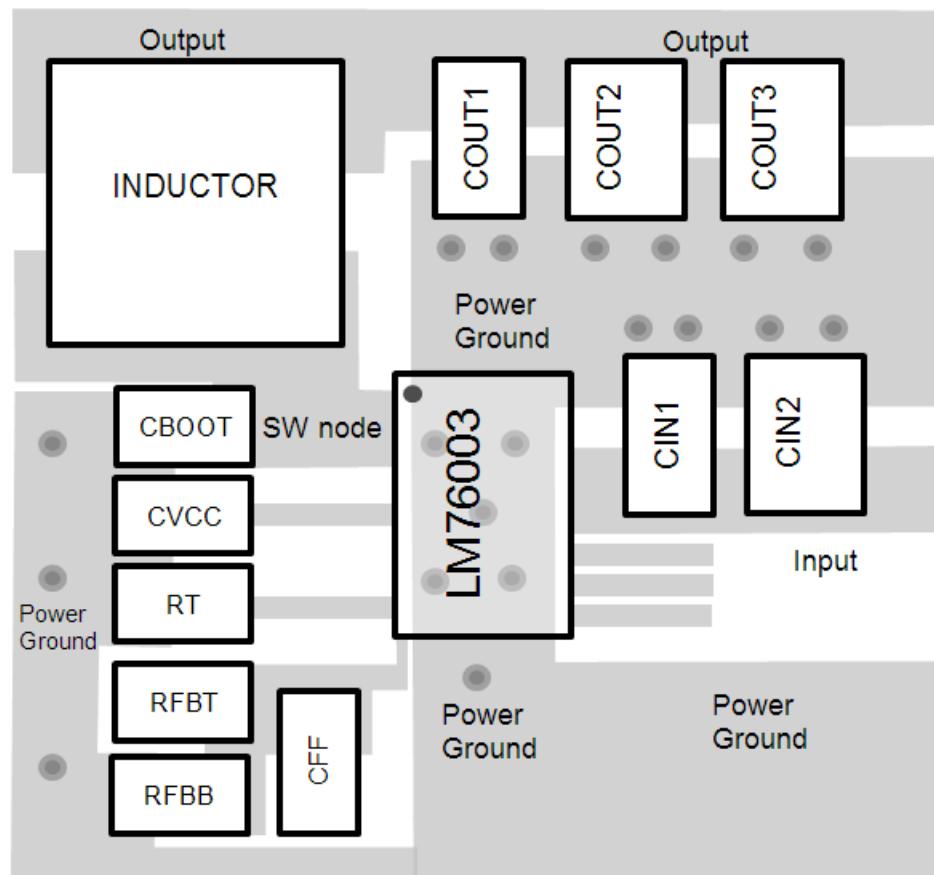

| 6.3      | Recommended Operating Conditions       | 5  | 10.2      | Layout Example                                          | 45 |

| 6.4      | Thermal Information                    | 6  | 10.3      | Thermal Design                                          | 46 |

| 6.5      | Electrical Characteristics             | 6  | <b>11</b> | <b>Device and Documentation Support</b>                 | 47 |

| 6.6      | Timing Characteristics                 | 8  | 11.1      | Device Support                                          | 47 |

| 6.7      | Switching Characteristics              | 8  | 11.2      | Receiving Notification of Documentation Updates         | 47 |

| 6.8      | System Characteristics                 | 9  | 11.3      | Support Resources                                       | 47 |

| 6.9      | Typical Characteristics                | 10 | 11.4      | Trademarks                                              | 47 |

| <b>7</b> | <b>Detailed Description</b>            | 12 | 11.5      | Electrostatic Discharge Caution                         | 47 |

| 7.1      | Overview                               | 12 | 11.6      | Glossary                                                | 47 |

| 7.2      | Functional Block Diagram               | 12 | <b>12</b> | <b>Mechanical, Packaging, and Orderable Information</b> | 47 |

## 4 Revision History

### Changes from Revision A (November 2018) to Revision B

|                                                                                                                                                   |  | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--|------|

| • Updated the <i>Thermal Information</i> table                                                                                                    |  | 6    |

| • Changed <i>Figure 17</i>                                                                                                                        |  | 18   |

| • Changed "the PGOOD switch is turned off" to "the PGOOD switch is turned on" in the <i>Power Good and Overvoltage Protection (PGOOD)</i> section |  | 20   |

### Changes from Original (October 2018) to Revision A

|                                                                                          |  | Page |

|------------------------------------------------------------------------------------------|--|------|

| • Deleted "Operating" from "Junction temperature row" in <i>Absolute Maximum Ratings</i> |  | 5    |

| • Deleted Operating junction $T_J$ from <i>Recommended Operating Conditions</i>          |  | 5    |

| • Updated the <i>Power Good and Overvoltage Protection (PGOOD)</i> section               |  | 20   |

| • Updated title of <i>Table 2</i>                                                        |  | 25   |

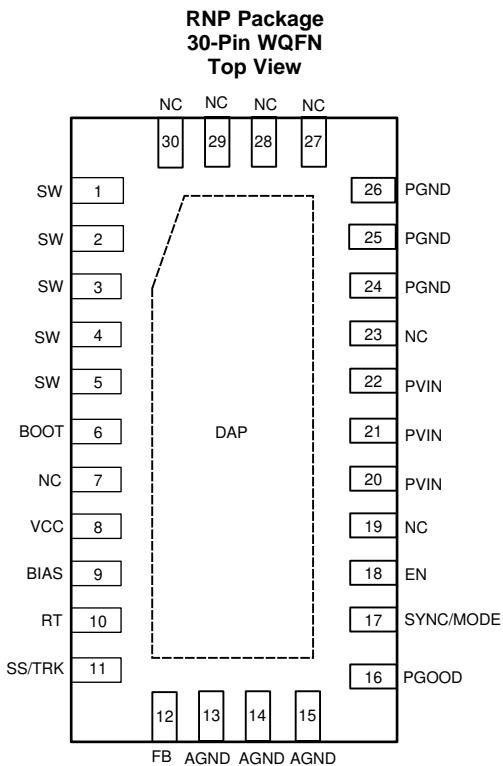

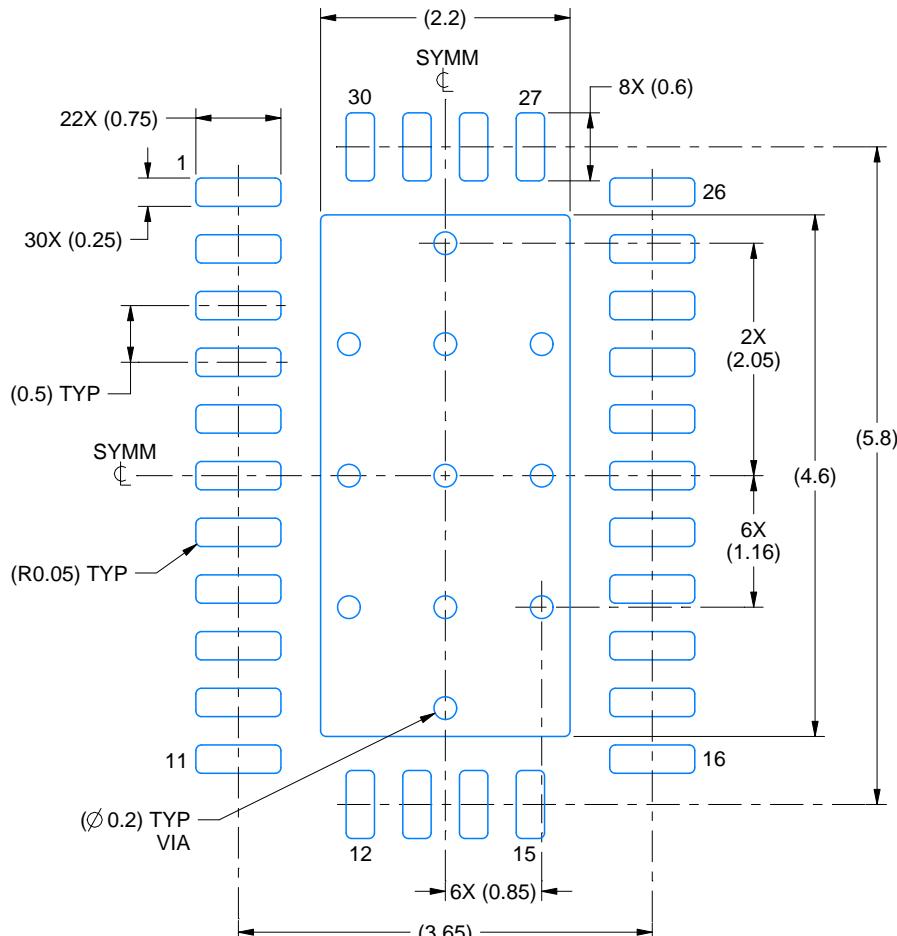

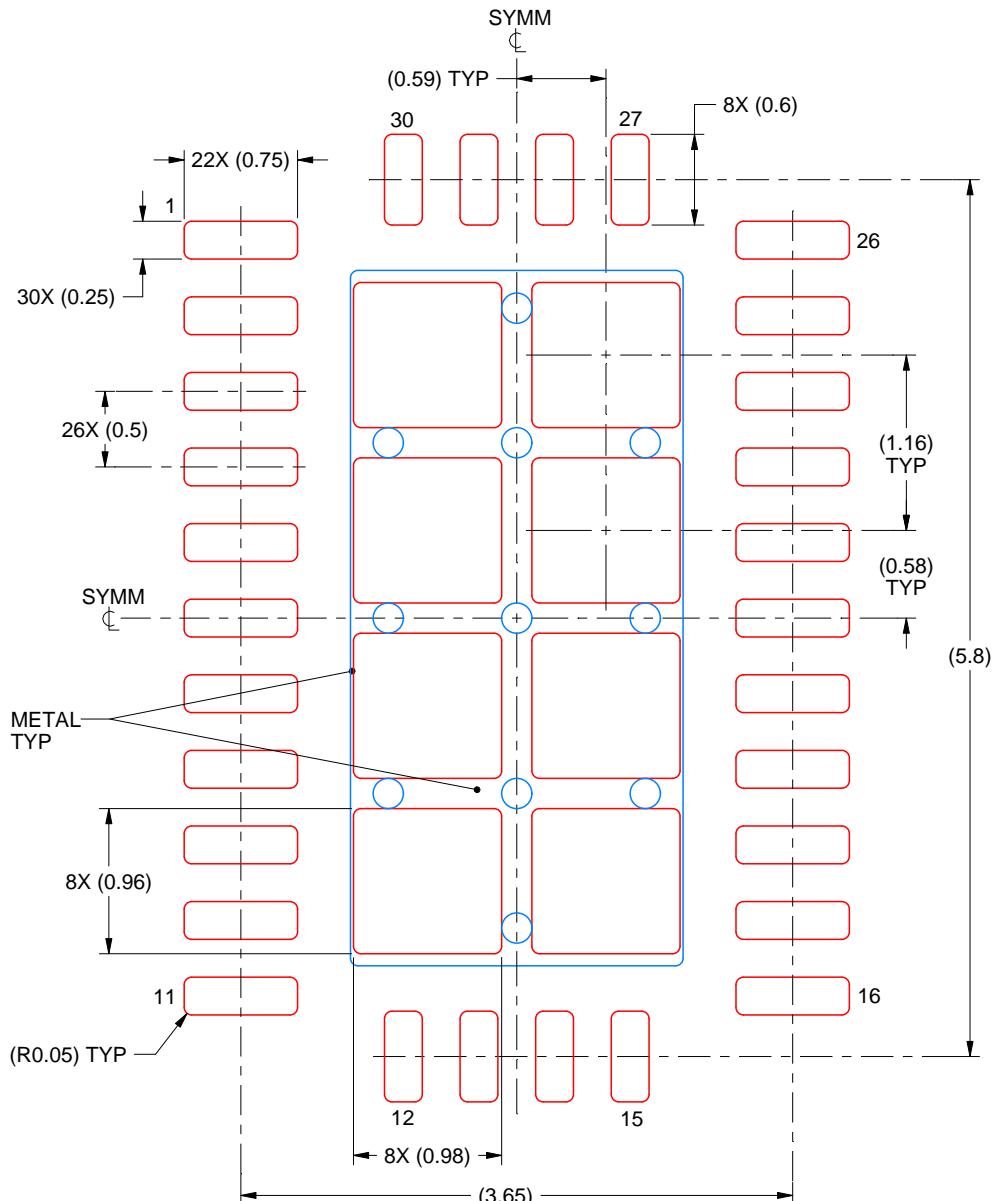

## 5 Pin Configuration and Functions

### Pin Functions

| PIN                       |           | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------|-----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                       | NAME      |                    |                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1, 2, 3, 4, 5             | SW        | P                  | Switching output of the regulator. Internally connected to source of the HS FET and drain of the LS FET. Connect to power inductor and boot-strap capacitor.                                                                                                                                                                                                                                                 |

| 6                         | BOOT      | P                  | Boot-strap capacitor connection for high-side driver. Connect a high-quality 470-nF capacitor from this pin to the SW pin.                                                                                                                                                                                                                                                                                   |

| 7, 19, 23, 27, 28, 29, 30 | NC        | —                  | Not internally connected. Connect to ground copper on PCB to improve heat-sinking of the device and board level reliability.                                                                                                                                                                                                                                                                                 |

| 8                         | VCC       | P                  | Output of internal bias supply. Used as supply to internal control circuits. Connect a high-quality 2.2- $\mu$ F capacitor from this pin to GND. TI does not recommended loading this pin by external circuitry.                                                                                                                                                                                             |

| 9                         | BIAS      | P                  | Optional BIAS LDO supply input. TI recommends tying this to $V_{OUT}$ when $3.3\text{ V} \leq V_{OUT} \leq 18\text{ V}$ , or tying to an external 3.3-V or 5-V rail if available, to improve efficiency. When used, place a 1- $\mu$ F capacitor from this terminal to ground. Tie to ground when not in use.                                                                                                |

| 10                        | RT        | A                  | Switching frequency setting pin. Place a resistor from this pin to ground to set the switching frequency. If floating, the default switching frequency is 500 kHz. Do not short to ground.                                                                                                                                                                                                                   |

| 11                        | SS/TRK    | A                  | Soft-start-control pin. Leave this pin floating to use the 6.3-ms internal soft-start ramp. An external capacitor can be connected from this pin to ground to extend the soft-start time. A 2- $\mu$ A current sourced from this pin can charge the capacitor to provide the ramp. Connect to external ramp for tracking. Do not short to ground.                                                            |

| 12                        | FB        | A                  | Feedback input for output voltage regulation. Connect a resistor divider to set the output voltage. Never short this terminal to ground during operation.                                                                                                                                                                                                                                                    |

| 16                        | PGOOD     | A                  | Open-drain power-good flag output. Connect to suitable voltage supply through a current limiting resistor. High = $V_{OUT}$ regulation OK, Low = $V_{OUT}$ regulation fault. PGOOD = Low when EN = Low.                                                                                                                                                                                                      |

| 17                        | SYNC/MODE | A                  | Synchronization input and mode setting pin. Do not float, tie to ground if not used. Tie to ground: DCM/PFM operation under light loads, improved efficiency; tie to logic high: forced PWM under light loads, constant switching frequency over load; tie to external clock source: synchronize switching action to the clock, forced PWM under light loads. Triggers on the rising edge of external clock. |

| 18                        | EN        | A                  | Precision-enable input to regulator. Do not float. High = on, Low = off. Can be tied to $V_{IN}$ . Precision-enable input allows adjustable UVLO by external resistor divider.                                                                                                                                                                                                                               |

| 13, 14, 15                | AGND      | G                  | Analog ground. Ground reference for internal references and logic. All electrical parameters are measured with respect to this pin. Connect to system ground on PCB.                                                                                                                                                                                                                                         |

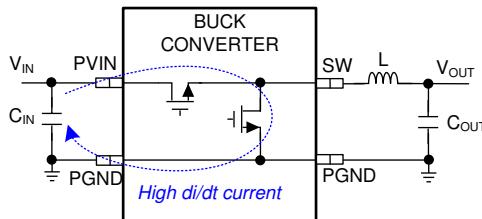

| 20, 21, 22                | PVIN      | P                  | Supply input to internal bias LDO and HS FET. Connect to input supply and input bypass capacitors $C_{IN}$ . $C_{IN}$ must be placed right next to this pin and PGND and connected with short traces.                                                                                                                                                                                                        |

| 24, 25, 26                | PGND      | G                  | Power ground, connected to the source of LS FET internally. Connect to system ground, DAP/EP, AGND, ground side of $C_{IN}$ and $C_{OUT}$ . Path to $C_{IN}$ must be as short as possible.                                                                                                                                                                                                                   |

| EP                        | DAP       | —                  | Low impedance connection to AGND. Connect to system ground on PCB. Major heat dissipation path for the die. Must be used for heat sinking by soldering to ground copper on PCB. Thermal vias are preferred.                                                                                                                                                                                                  |

(1) A = Analog, O = Output, I = Input, G = Ground, P = Power

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range of  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  (unless otherwise noted)<sup>(1)</sup>

|                                | PARAMETER                             | MIN  | MAX                               | UNIT               |

|--------------------------------|---------------------------------------|------|-----------------------------------|--------------------|

| Input voltages                 | PVIN to PGND                          | -0.3 | 65                                | V                  |

|                                | EN to AGND                            | -0.3 | $V_{IN} + 0.3$                    |                    |

|                                | FB, RT, SS/TRK to AGND                | -0.3 | 5                                 |                    |

|                                | PGOOD to AGND                         | -0.1 | 20                                |                    |

|                                | SYNC to AGND                          | -0.3 | 5.5                               |                    |

|                                | BIAS to AGND                          | -0.3 | Lower of ( $V_{IN} + 0.3$ ) or 30 |                    |

|                                | AGND to PGND                          | -0.3 | 0.3                               |                    |

| Output voltages                | SW to PGND                            | -0.3 | $V_{IN} + 0.3$                    | V                  |

|                                | SW to PGND less than 10-ns transients | -3.5 | 65                                |                    |

|                                | BOOT to SW                            | -0.3 | 5.5                               |                    |

|                                | VCC to AGND                           | -0.3 | 5.5                               |                    |

| Junction temperature, $T_J$    |                                       | -40  | 150                               | $^{\circ}\text{C}$ |

| Storage temperature, $T_{stg}$ |                                       | -65  | 150                               | $^{\circ}\text{C}$ |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|             |                         |                                                         | VALUE      | UNIT |

|-------------|-------------------------|---------------------------------------------------------|------------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> | $\pm 2000$ | V    |

|             |                         | Charged-device model (CDM), per AEC Q100-011            | $\pm 750$  | V    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                |                        | MIN  | MAX                               | UNIT |

|----------------|------------------------|------|-----------------------------------|------|

| Input voltages | PVIN to PGND           | 3.5  | 60                                | V    |

|                | EN                     | 0    | $V_{IN}$                          |      |

|                | FB                     | 0    | 4.5                               |      |

|                | PGOOD                  | 0    | 18                                |      |

|                | BIAS input not used    | 0    | 0.3                               |      |

|                | BIAS input used        | 0    | Lower of ( $V_{IN} + 0.3$ ) or 24 |      |

|                | AGND to PGND           | -0.1 | 0.1                               |      |

| Output voltage | $V_{OUT}$              | 1    | 95% of $V_{IN}$                   | V    |

| Output current | $I_{OUT}$ , LM76002-Q1 | 0    | 2.5                               | A    |

|                | $I_{OUT}$ , LM76003-Q1 | 0    | 3.5                               |      |

(1) Recommended operating rating indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For ensured specifications, see *Electrical Characteristics*.

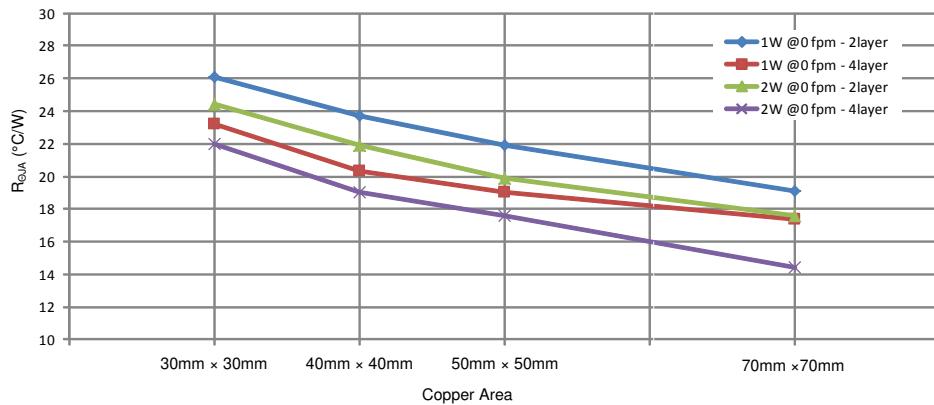

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | LM76002/LM76003 | UNIT |

|-------------------------------|----------------------------------------------|-----------------|------|

|                               |                                              | RNP (WQFN)      |      |

|                               |                                              | 30 PINS         |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 29.6            | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 17.6            | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 9.1             | °C/W |

| $\psi_{JT}$                   | Junction-to-top characterization parameter   | 0.2             | °C/W |

| $\psi_{JB}$                   | Junction-to-board characterization parameter | 9.0             | °C/W |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | 1.0             | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

## 6.5 Electrical Characteristics

Limits apply over the recommended operating junction temperature ( $T_J$ ) range of  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise stated. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{IN} = 24\text{ V}$ .

| PARAMETER                               | TEST CONDITIONS                                                      | MIN                                                                                     | TYP   | MAX   | UNIT          |    |

|-----------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|---------------|----|

| <b>SUPPLY VOLTAGE (PVIN PINS)</b>       |                                                                      |                                                                                         |       |       |               |    |

| $V_{IN}$                                | Operating input voltage range                                        |                                                                                         | 3.5   | 60    | V             |    |

| $I_{SD}$                                | Shutdown quiescent current; measured at PVIN pin <sup>(1)</sup>      | $V_{EN} = 0\text{ V}$<br>$T_J = 25^{\circ}\text{C}$                                     | 1.2   | 10    | $\mu\text{A}$ |    |

| $I_{Q\_NONSW}$                          | Operating quiescent current from $V_{IN}$ (non-switching)            | $V_{EN} = 2\text{ V}$ , $V_{FB} = 1.5\text{ V}$ , $V_{BIAS} = 3.3\text{ V}$<br>external | 0.9   | 12    | $\mu\text{A}$ |    |

| <b>ENABLE (EN PIN)</b>                  |                                                                      |                                                                                         |       |       |               |    |

| $V_{EN\_VCC\_H}$                        | Enable input high level for $V_{CC}$ output                          | $V_{EN}$ rising                                                                         |       | 1.2   | V             |    |

| $V_{EN\_VCC\_L}$                        | Enable input low level for $V_{CC}$ output                           | $V_{EN}$ falling                                                                        | 0.3   |       | V             |    |

| $V_{EN\_VOUT\_H}$                       | Enable input high level for $V_{OUT}$                                | $V_{EN}$ rising                                                                         | 1.14  | 1.204 | 1.25          | V  |

| $V_{EN\_VOUT\_HYS}$                     | Enable input hysteresis for $V_{OUT}$                                | $V_{EN}$ falling hysteresis                                                             |       | -150  | mV            |    |

| $I_{LKG\_EN}$                           | Enable input leakage current                                         | $V_{EN} = 2\text{ V}$                                                                   | 1.4   | 200   | nA            |    |

| <b>INTERNAL LDO (VCC PIN, BIAS PIN)</b> |                                                                      |                                                                                         |       |       |               |    |

| $V_{CC}$                                | Internal $V_{CC}$ voltage                                            | PWM operation                                                                           |       | 3.29  | V             |    |

|                                         |                                                                      | PFM operation                                                                           |       | 3.1   | V             |    |

| $V_{CC\_UVLO}$                          | Internal $V_{CC}$ undervoltage lockout                               | $V_{CC}$ rising                                                                         | 2.96  | 3.14  | 3.27          | V  |

|                                         |                                                                      | $V_{CC}$ falling hysteresis                                                             |       | -565  |               | mV |

| $V_{BIAS\_ON}$                          | Input changeover                                                     | $V_{BIAS}$ rising                                                                       |       | 3.11  | 3.25          | V  |

|                                         |                                                                      | $V_{BIAS}$ falling hysteresis                                                           |       | -63   |               | mV |

| $I_{BIAS\_NONSW}$                       | Operating quiescent current from external $V_{BIAS}$ (non-switching) | $V_{EN} = 2\text{ V}$ , $V_{FB} = 1.5\text{ V}$ , $V_{BIAS} = 3.3\text{ V}$<br>external | 21    | 50    | $\mu\text{A}$ |    |

| <b>VOLTAGE REFERENCE (FB PIN)</b>       |                                                                      |                                                                                         |       |       |               |    |

| $V_{FB}$                                | Feedback voltage                                                     | PWM mode                                                                                | 0.987 | 1.006 | 1.017         | V  |

| $I_{LKG\_FB}$                           | Input leakage current at FB pin                                      | $V_{FB} = 1\text{ V}$                                                                   | 0.2   | 60    | nA            |    |

(1) Shutdown current includes leakage current of the switching transistors.

## Electrical Characteristics (continued)

Limits apply over the recommended operating junction temperature ( $T_J$ ) range of  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise stated. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{IN} = 24\text{ V}$ .

| PARAMETER                                                | TEST CONDITIONS                                 | MIN                                                                                       | TYP  | MAX  | UNIT                 |

|----------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|----------------------|

| <b>HIGH SIDE DRIVER (BOOT PIN)</b>                       |                                                 |                                                                                           |      |      |                      |

| $V_{BOOT\_UVLO}$                                         | BOOT - SW undervoltage lockout                  | 1.6                                                                                       | 2.2  | 2.7  | V                    |

| <b>CURRENT LIMITS AND HICCUP</b>                         |                                                 |                                                                                           |      |      |                      |

| $I_{HS\_LIMIT}^{(2)}$                                    | Short-circuit, high-side current limit          | LM76002-Q1                                                                                | 3.2  | 4.2  | 5.3                  |

|                                                          |                                                 | LM76003-Q1                                                                                | 4.35 | 5.5  | 6.8                  |

| $I_{LS\_LIMIT}^{(2)}$                                    | Low-side current limit                          | LM76002-Q1                                                                                | 2.3  | 3.2  | 4.2                  |

|                                                          |                                                 | LM76003-Q1                                                                                | 3.4  | 4.2  | 5.3                  |

| $I_{NEG\_LIMIT}$                                         | Negative current limit                          | LM76002-Q1                                                                                |      | -2.5 |                      |

|                                                          |                                                 | LM76003-Q1                                                                                |      | -3.3 |                      |

| $V_{HICCUP}$                                             | Hiccup threshold on FB pin                      |                                                                                           | 0.38 | 0.42 | 0.46                 |

| $I_{L\_ZC}$                                              | Zero cross-current limit                        |                                                                                           |      | 0.05 | A                    |

| <b>SOFT START (SS/TRK PIN)</b>                           |                                                 |                                                                                           |      |      |                      |

| $I_{SSC}$                                                | Soft-start charge current                       |                                                                                           | 1.8  | 2    | 2.2                  |

| $R_{SSD}$                                                | Soft-start discharge resistance                 | UVLO, TSD, OCP; or $EN = 0\text{ V}$                                                      |      | 2    | $\text{k}\Omega$     |

| <b>POWER GOOD (PGOOD PIN) and OVERVOLTAGE PROTECTION</b> |                                                 |                                                                                           |      |      |                      |

| $V_{PGOOD\_OV}$                                          | Power-good overvoltage threshold                | % of FB voltage                                                                           | 106% | 110% | 113%                 |

| $V_{PGOOD\_UV}$                                          | Power-good undervoltage threshold               | % of FB voltage                                                                           | 86%  | 90%  | 93%                  |

| $V_{PGOOD\_HYS}$                                         | Power-good hysteresis                           | % of FB voltage                                                                           |      | 2.5% |                      |

| $V_{PGOOD\_VALID}$                                       | Minimum input voltage for proper PGOOD function | 50- $\mu\text{A}$ pullup to PGOOD pin, $V_{EN} = 0\text{ V}$ , $T_J = 25^{\circ}\text{C}$ |      | 1.3  | 2                    |

| $R_{PGOOD}$                                              | Power-good on-resistance                        | $V_{EN} = 2.5\text{ V}$                                                                   |      | 40   | 100                  |

|                                                          |                                                 | $V_{EN} = 0\text{ V}$                                                                     |      | 30   | 90                   |

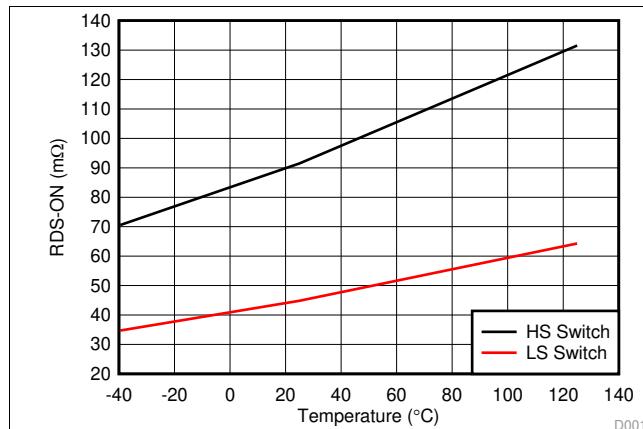

| <b>MOSFETS</b>                                           |                                                 |                                                                                           |      |      |                      |

| $R_{DS\_ON\_HS}^{(3)}$                                   | High-side MOSFET on-resistance                  | $I_{OUT} = 1\text{ A}$ , $V_{BIAS} = V_{OUT} = 3.3\text{ V}$                              |      | 95   | $150\text{ m}\Omega$ |

| $R_{DS\_ON\_LS}^{(3)}$                                   | Low-side MOSFET on-resistance                   | $I_{OUT} = 1\text{ A}$ , $V_{BIAS} = V_{OUT} = 3.3\text{ V}$                              |      | 45   | $85\text{ m}\Omega$  |

| <b>THERMAL SHUTDOWN</b>                                  |                                                 |                                                                                           |      |      |                      |

| $T_{SD}^{(4)}$                                           | Thermal shutdown threshold                      | Shutdown threshold                                                                        |      | 160  |                      |

|                                                          | Recovery threshold                              |                                                                                           |      | 135  | $^{\circ}\text{C}$   |

(2) This current limit was measured as the internal comparator trip point. Due to inherent delays in the current limit comparator and drivers, the peak current limit measured in closed loop with faster slew rate will be larger, and valley current limit will be lower.

(3) Measured at pins.

(4) Ensured by design.

## 6.6 Timing Characteristics

|                                                          |                                                     |                                                      | MIN | NOM | MAX | UNIT   |

|----------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|-----|-----|-----|--------|

| <b>CURRENT LIMITS AND HICCUP</b>                         |                                                     |                                                      |     |     |     |        |

| $N_{OC}^{(1)}$                                           | Number of switching cycles before hiccup is tripped |                                                      |     | 128 |     | Cycles |

| $t_{OC}$                                                 | Overcurrent hiccup retry delay time                 |                                                      |     | 46  |     | ms     |

| <b>SOFT START (SS/TRK PIN)</b>                           |                                                     |                                                      |     |     |     |        |

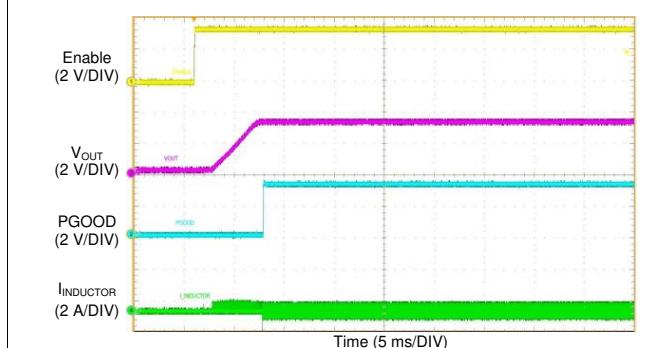

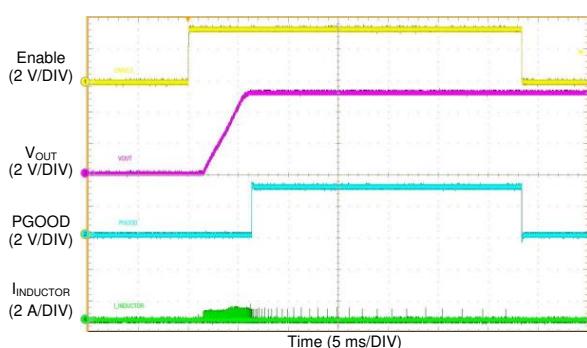

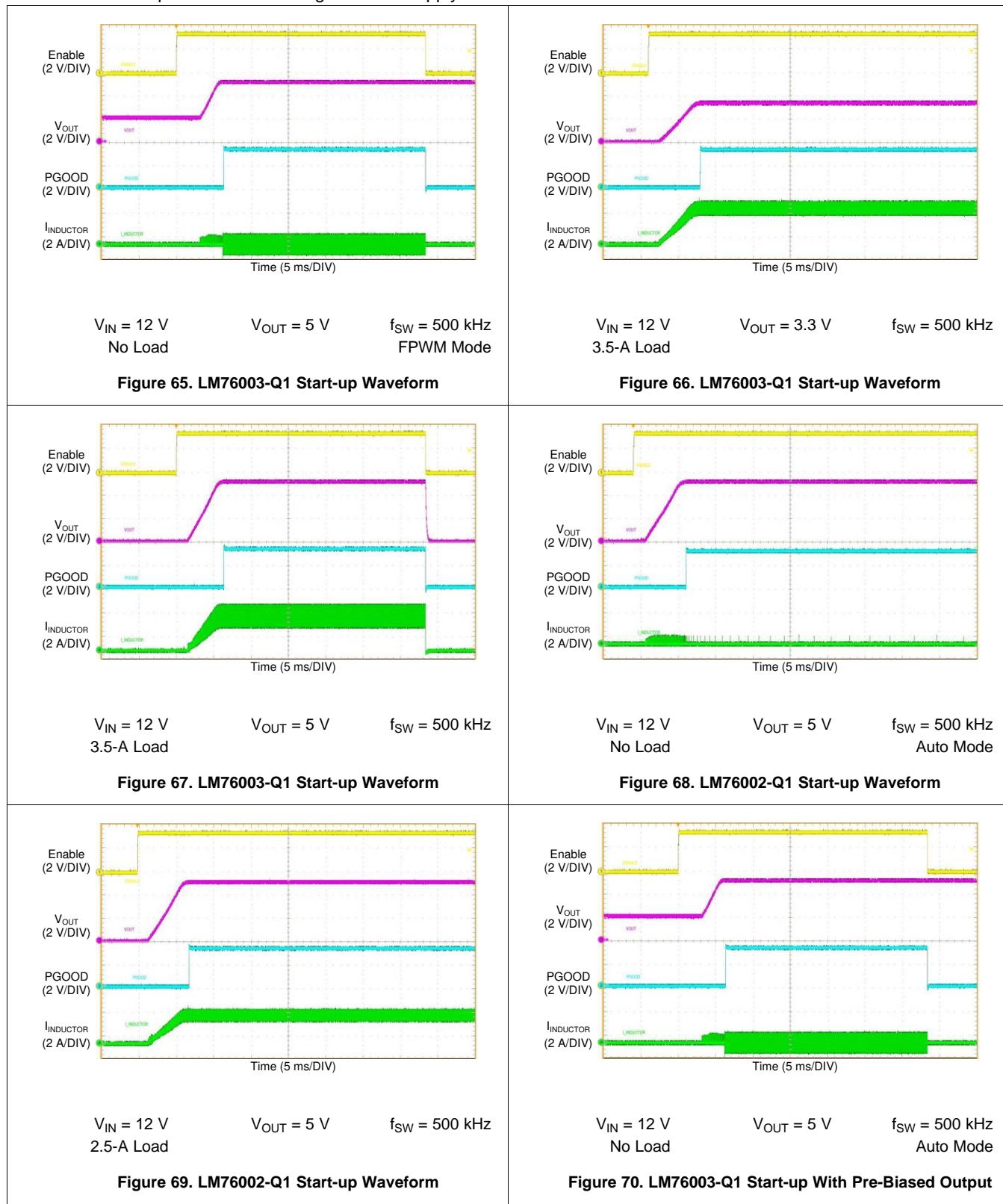

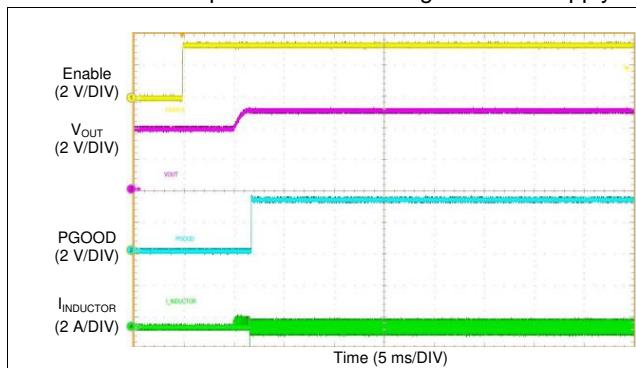

| $t_{SS}$                                                 | Internal soft-start time                            | CSS = OPEN, from EN rising edge to PGOOD rising edge | 3.5 | 6.3 |     | ms     |

| <b>POWER GOOD (PGOOD PIN) and OVERVOLTAGE PROTECTION</b> |                                                     |                                                      |     |     |     |        |

| $t_{PGOOD\_RISE}$                                        | PGOOD rising edge deglitch delay                    |                                                      | 80  | 140 | 200 | μs     |

| $t_{PGOOD\_FALL}$                                        | PGOOD falling edge deglitch delay                   |                                                      | 80  | 140 | 200 | μs     |

(1) Ensured by design.

## 6.7 Switching Characteristics

| PARAMETER                            | TEST CONDITIONS                               | MIN                                 | TYP  | MAX  | UNIT |     |

|--------------------------------------|-----------------------------------------------|-------------------------------------|------|------|------|-----|

| <b>PWM LIMITS (SW PINS)</b>          |                                               |                                     |      |      |      |     |

| $t_{ON-MIN}$                         | Minimum switch on-time                        |                                     | 65   | 95   | ns   |     |

| $t_{OFF-MIN}$                        | Minimum switch off-time                       |                                     | 95   | 130  | ns   |     |

| $t_{ON-MAX}$                         | Maximum switch on-time                        | HS timeout in dropout               | 3.8  | 8    | 11.4 | μs  |

| <b>OSCILLATOR (RT and SYNC PINS)</b> |                                               |                                     |      |      |      |     |

| $f_{OSC}$                            | Internal oscillator frequency                 | $R_T = \text{Open}$                 | 440  | 500  | 560  | kHz |

| $f_{ADJ}$                            | Minimum adjustable frequency by $R_T$ or SYNC | $R_T = 133 \text{ k}\Omega, 0.1\%$  | 270  | 300  | 330  | kHz |

|                                      | Maximum adjustable frequency by $R_T$ or SYNC | $R_T = 17.4 \text{ k}\Omega, 0.1\%$ | 1980 | 2200 | 2420 |     |

| $V_{SYNC\_HIGH}$                     | Sync input high level threshold               |                                     |      | 2    | V    |     |

| $V_{SYNC\_LOW}$                      | Sync input low level threshold                |                                     | 0.4  |      | V    |     |

| $V_{MODE\_HIGH}$                     | Mode input high level threshold for FPWM      |                                     | 0.42 |      | V    |     |

| $V_{MODE\_LOW}$                      | Mode input low level threshold for AUTO mode  |                                     | 0.4  |      | V    |     |

| $t_{SYNC\_MIN}$                      | Sync input minimum on- and off-time           |                                     | 80   |      | ns   |     |

## 6.8 System Characteristics

The following specifications apply to the circuit found in the typical *Simplified Schematic* with appropriate modifications (see [Table 2](#)). These parameters are not tested in production and represent typical performance only. Unless otherwise stated the following conditions apply:  $T_A = 25^\circ\text{C}$ ,  $V_{IN} = 24\text{ V}$ ,  $V_{OUT} = 3.3\text{ V}$ ,  $f_{SW} = 500\text{ kHz}$ .

| PARAMETER       |                                                                             | TEST CONDITIONS                                                                                                                         | MIN | TYP   | MAX | UNIT          |

|-----------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|---------------|

| $V_{FB\_PFM}$   | Output voltage offset at no load in auto mode                               | $V_{IN} = 3.8\text{ V}$ to $36\text{ V}$ , $V_{SYNC} = 0\text{ V}$ , auto mode<br>$I_{OUT} = 0\text{ A}$                                |     | 2%    |     |               |

| $V_{drop}$      | Minimum input to output voltage differential to maintain specified accuracy | $V_{OUT} = 5\text{ V}$ , $I_{OUT} = 1.5\text{ A}$ , $f_{SW} = 2.2\text{ MHz}$                                                           |     | 0.4   |     | V             |

| $I_{Q\_SW}$     | Operating quiescent current (switching)                                     | $V_{EN} = 3.3\text{ V}$ , $I_{OUT} = 0\text{ A}$ , $R_T = \text{open}$ , $V_{BIAS} = V_{OUT} = 3.3\text{ V}$ , $R_{FBT} = 1\text{ Meg}$ |     | 15    |     | $\mu\text{A}$ |

| $I_{PEAK\_MIN}$ | Minimum inductor peak current                                               | LM76002-Q1:<br>$V_{SYNC} = 0\text{ V}$ , $I_{OUT} = 10\text{ mA}$                                                                       |     | 0.5   | A   |               |

|                 |                                                                             | LM76003-Q1:<br>$V_{SYNC} = 0\text{ V}$ , $I_{OUT} = 10\text{ mA}$                                                                       |     | 0.7   |     |               |

| $I_{BIAS\_SW}$  | Operating quiescent current from external $V_{BIAS}$ (switching)            | $f_{SW} = 500\text{ kHz}$ , $I_{OUT} = 1\text{ A}$                                                                                      |     | 7     | mA  |               |

|                 |                                                                             | $f_{SW} = 2.2\text{ MHz}$ , $I_{OUT} = 1\text{ A}$                                                                                      |     | 25    |     |               |

| $D_{MAX}$       | Maximum switch duty cycle                                                   | While in frequency foldback                                                                                                             |     | 97.5% |     |               |

| $t_{DEAD}$      | Dead time between high-side and low-side MOSFETs                            |                                                                                                                                         |     | 4     |     | ns            |

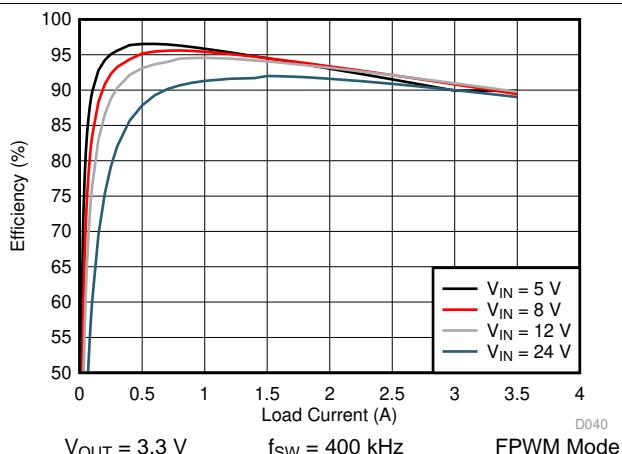

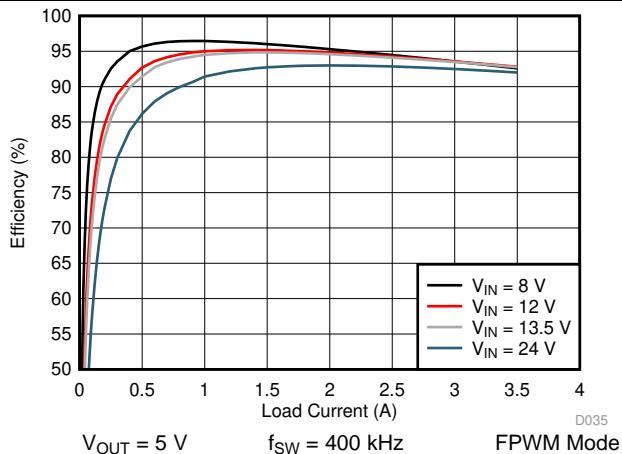

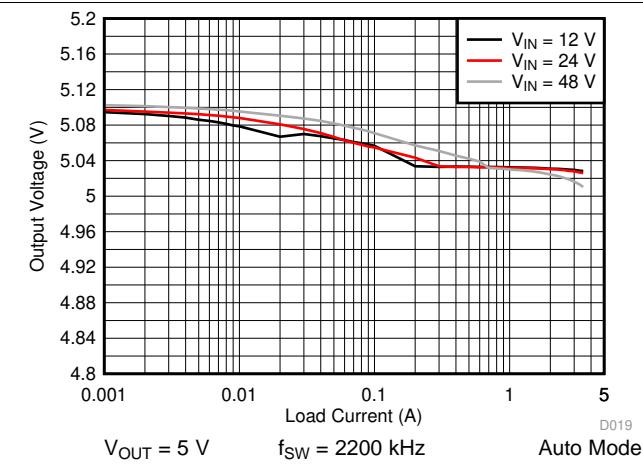

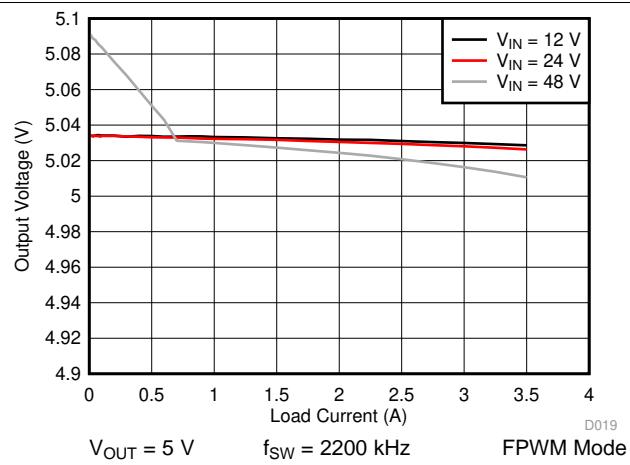

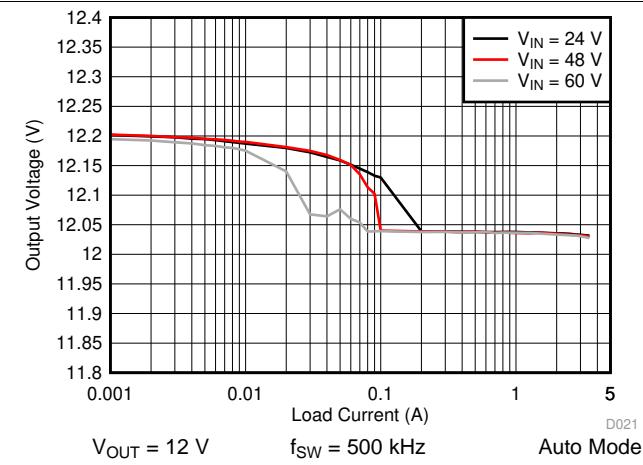

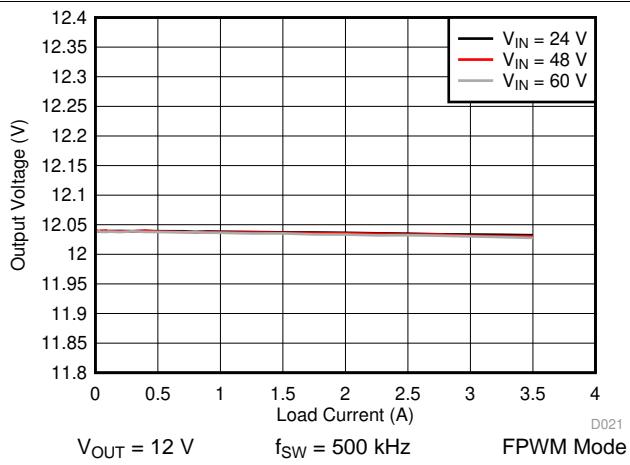

## 6.9 Typical Characteristics

Unless otherwise specified,  $V_{IN} = 24$  V. Curves represent most likely parametric norm at specified condition.

Figure 1. High-Side and Low-Side Switch  $R_{DS-ON}$

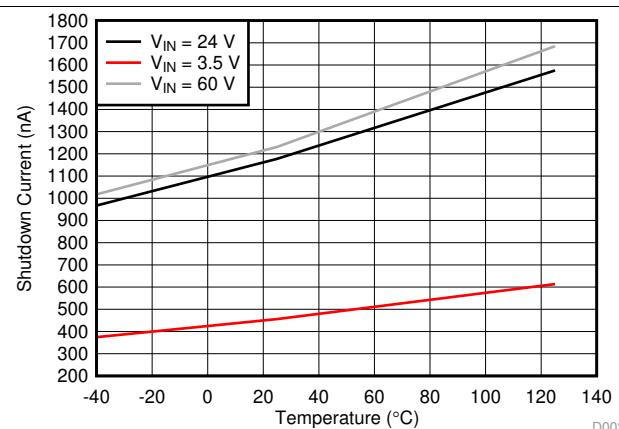

Figure 2. Shutdown Quiescent Current

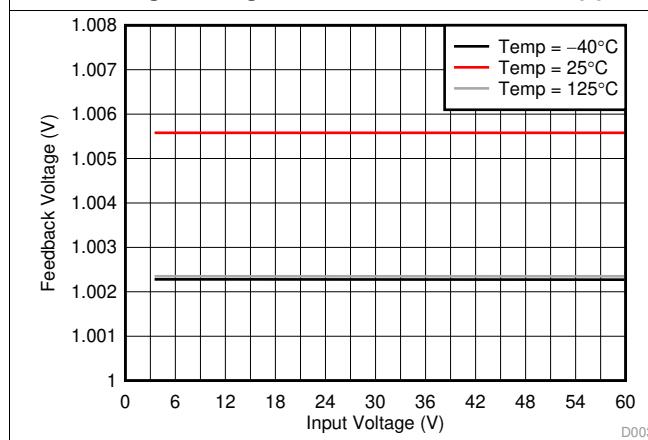

Figure 3. Feedback Voltage

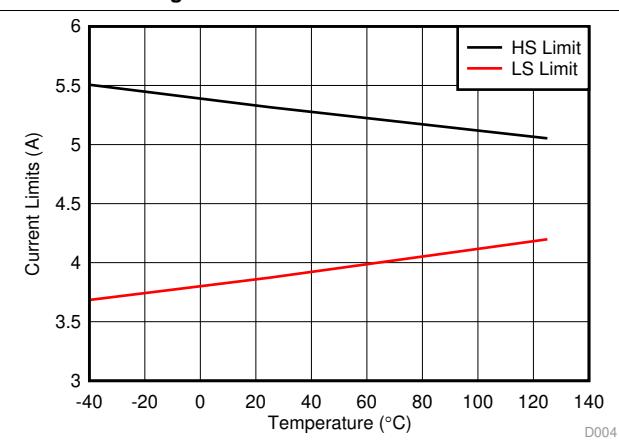

Figure 4. LM76003-Q1 High-Side and Low-Side Current Limits

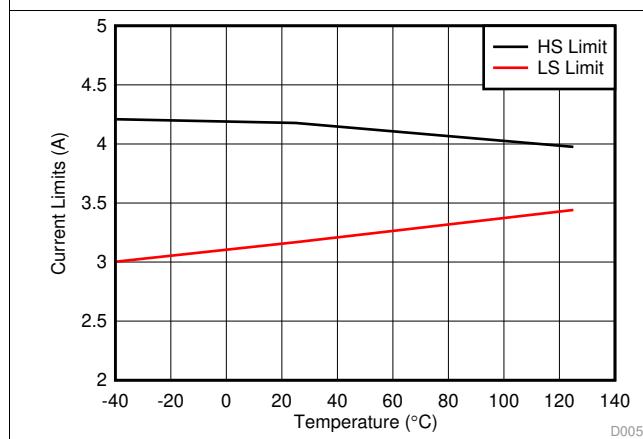

Figure 5. LM76002-Q1 High-Side and Low-Side Current Limits

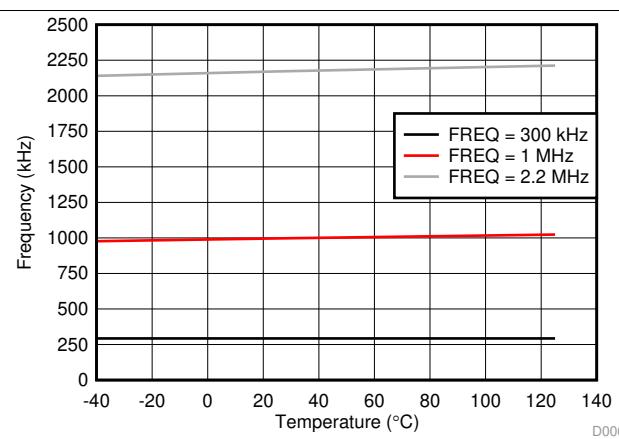

Figure 6. Switching Frequency Set by  $R_T$  Resistor

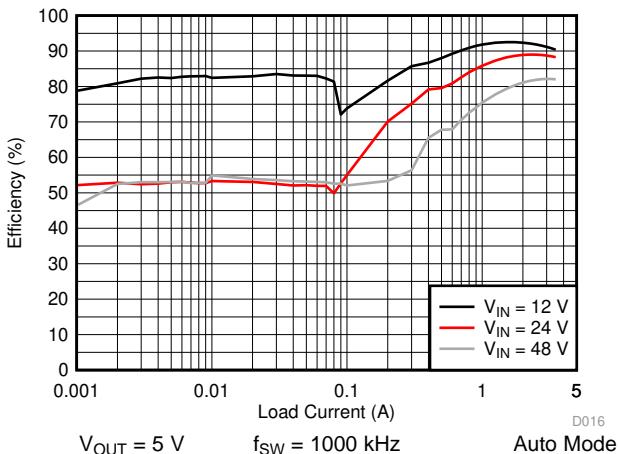

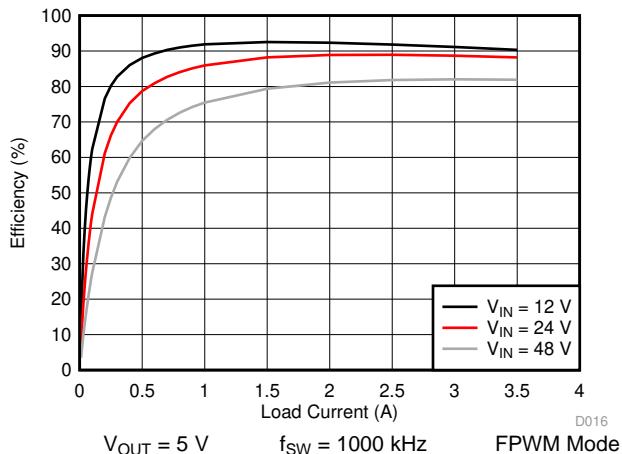

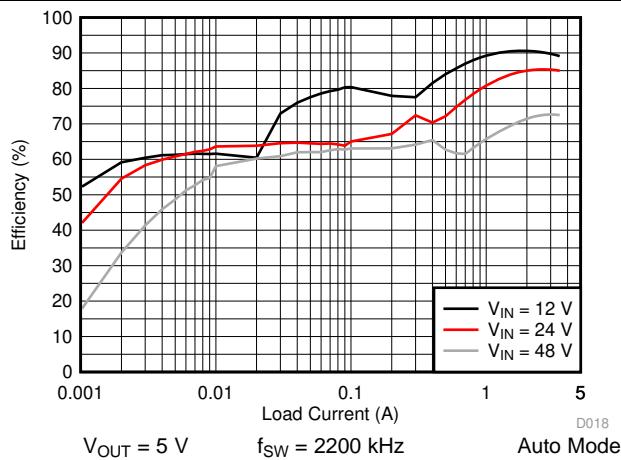

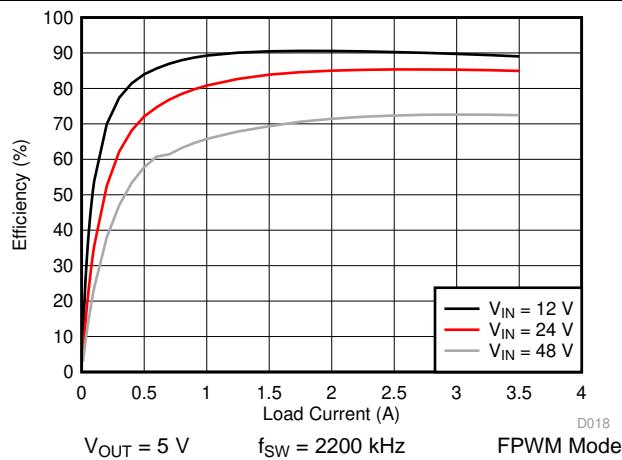

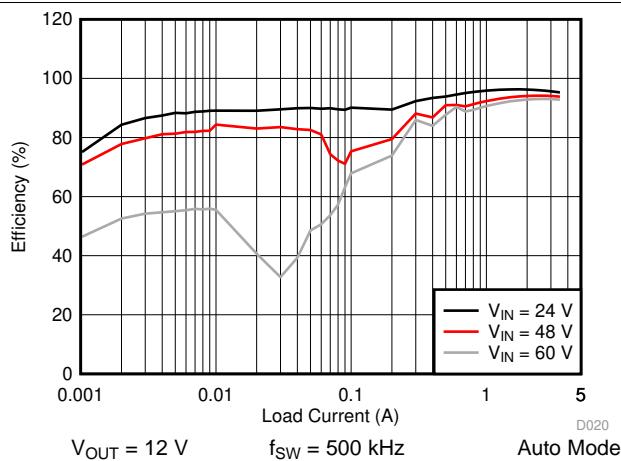

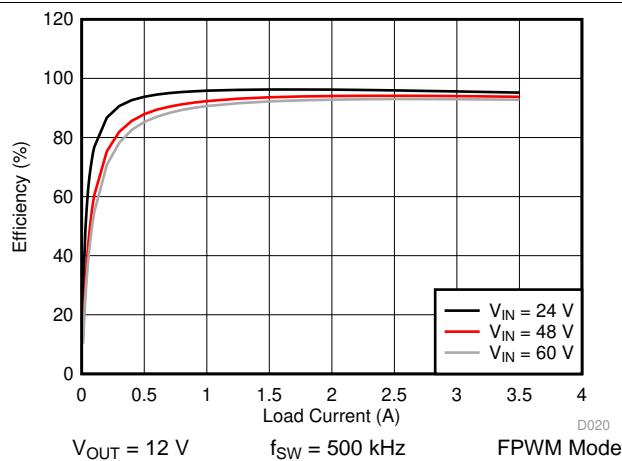

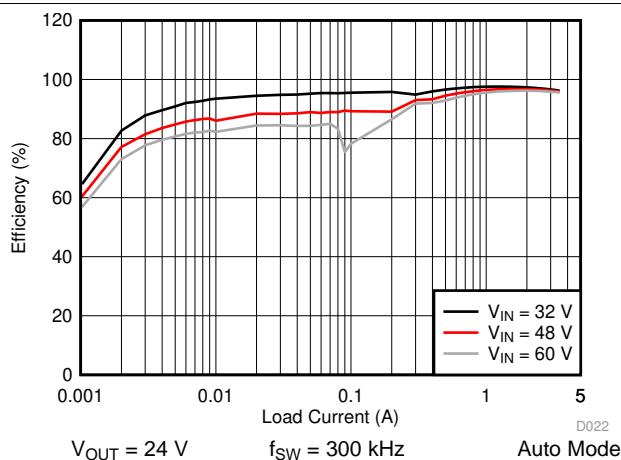

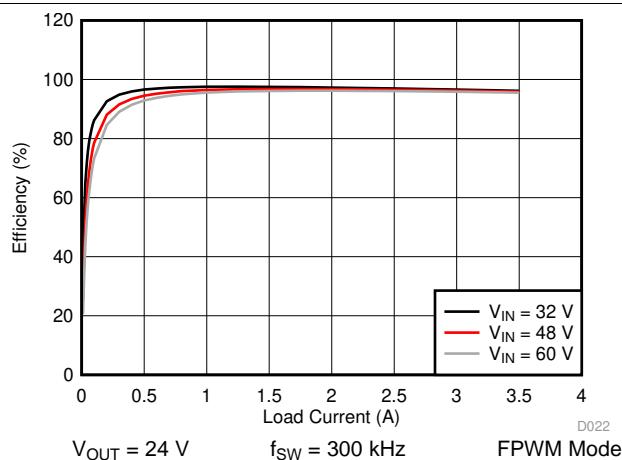

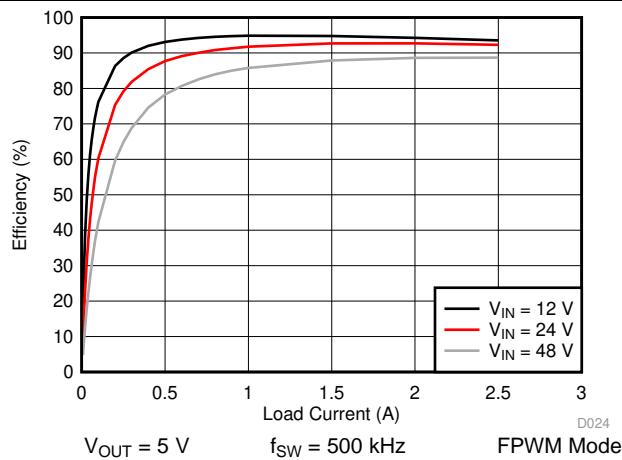

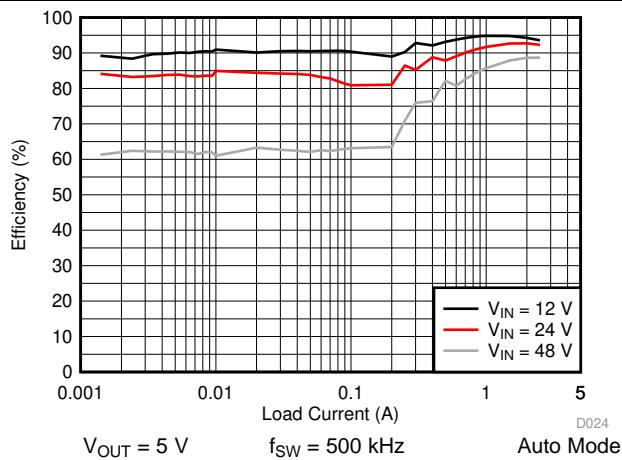

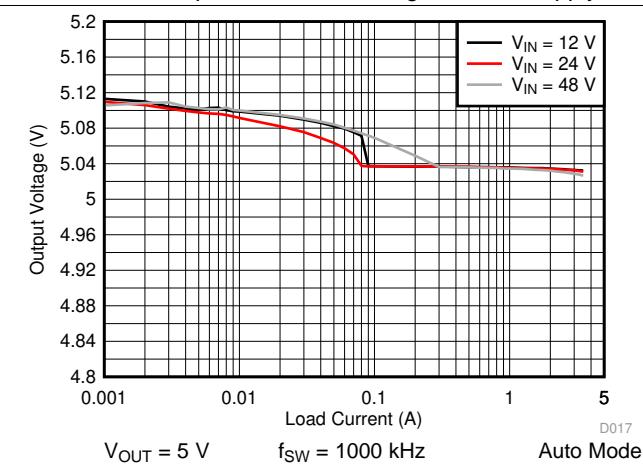

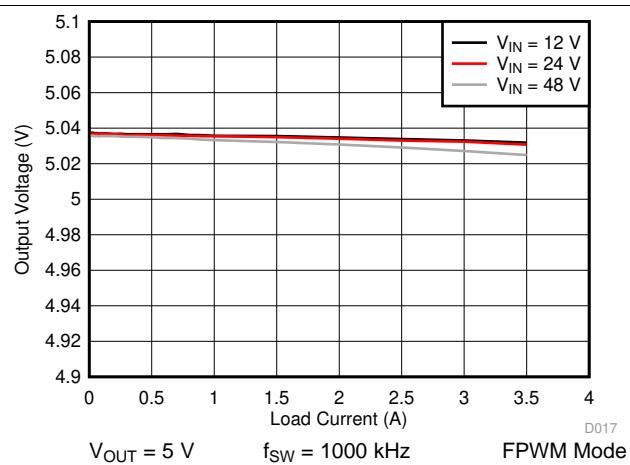

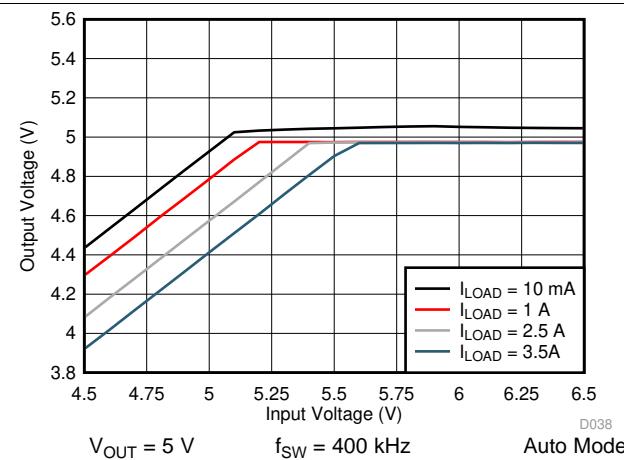

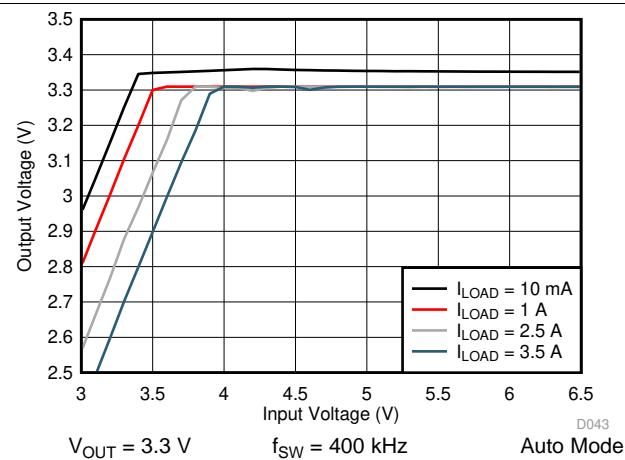

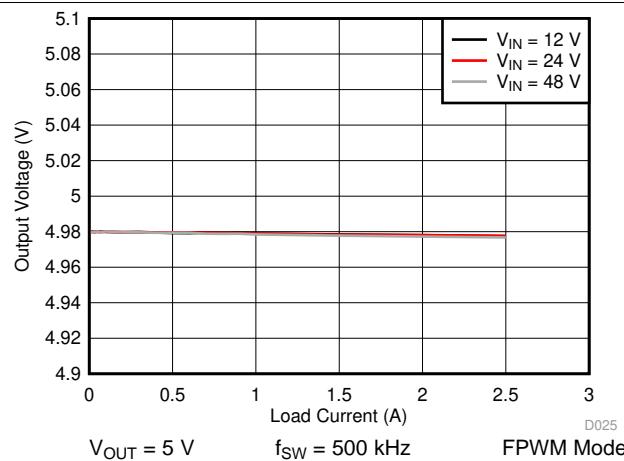

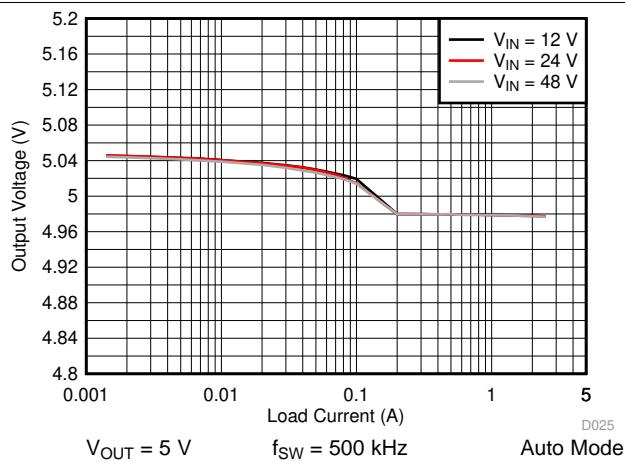

## Typical Characteristics (continued)

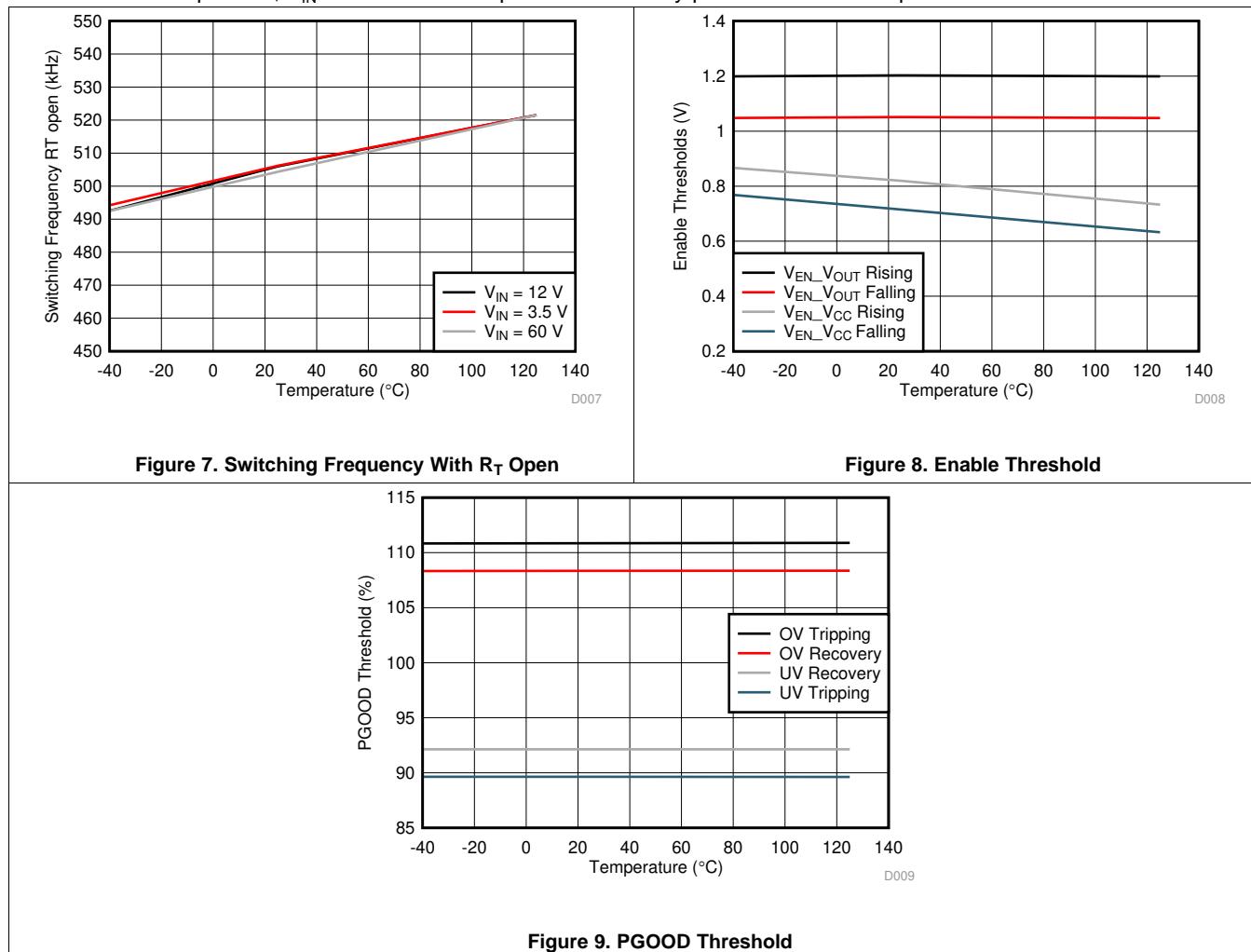

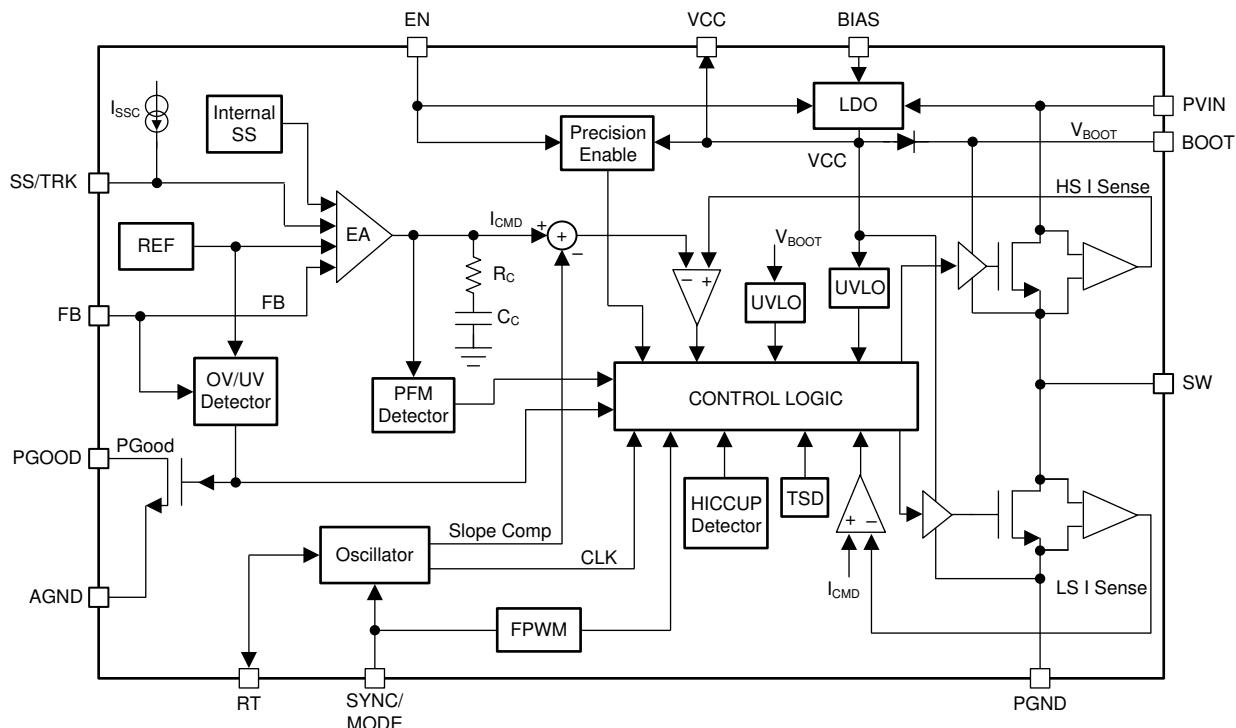

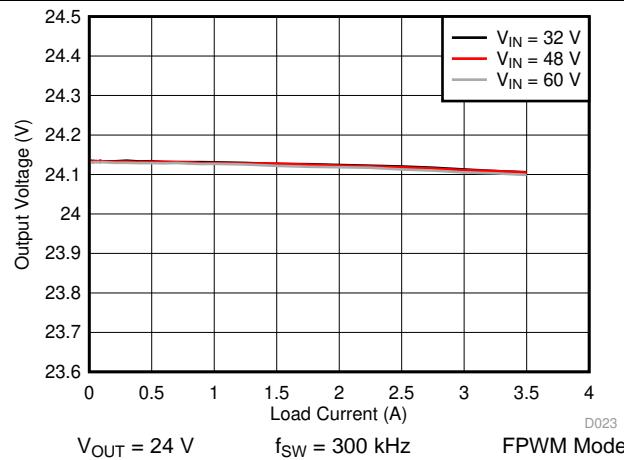

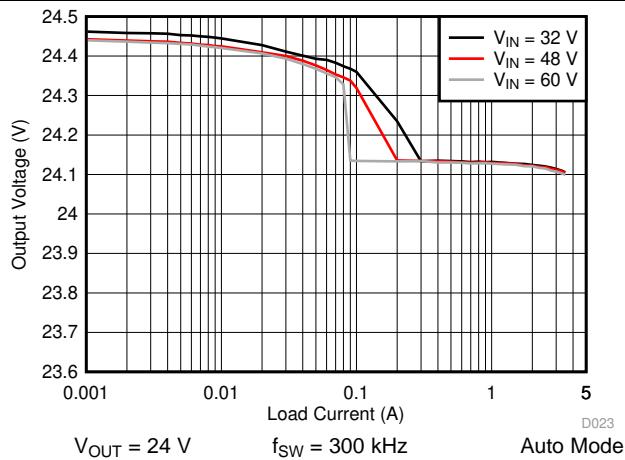

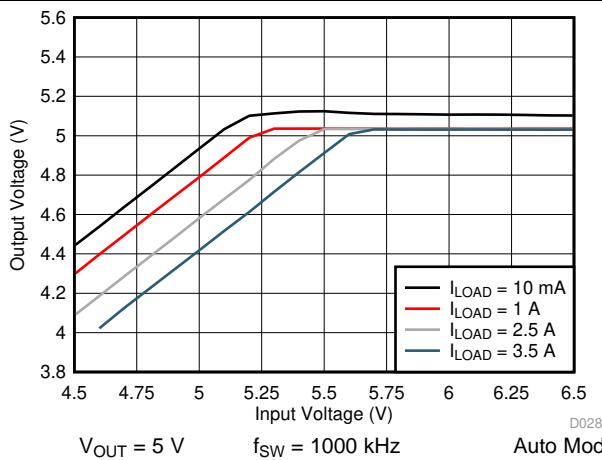

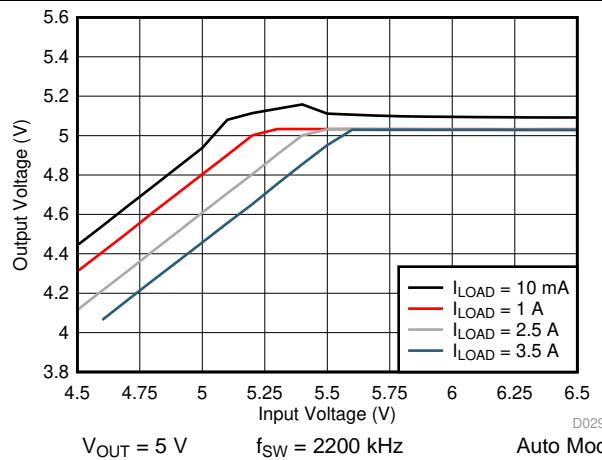

Unless otherwise specified,  $V_{IN} = 24$  V. Curves represent most likely parametric norm at specified condition.

## 7 Detailed Description

### 7.1 Overview

The LM76002-Q1/LM76003-Q1 regulator is an easy-to-use synchronous step-down DC-DC converter that operates from 3.5-V to 60-V supply voltage. The device is capable of delivering up to 2.5-A or 3.5-A DC load current with exceptional efficiency and thermal performance in a very small solution size.

The LM76002-Q1/LM76003-Q1 employs fixed-frequency peak-current-mode control with configurable discontinuous conduction mode (DCM) and pulse frequency modulation (PFM) mode at light load to achieve high efficiency across the load range. The device can also be configured as forced-PWM (FPWM) operation to keep constant switching frequency over the load range. The device is internally compensated, which reduces design time and requires fewer external components. The switching frequency is programmable from 300 kHz to 2.2 MHz by an external resistor. The LM76002-Q1/LM76003-Q1 is also capable of synchronization to an external clock operating within the 300-kHz to 2.2-MHz frequency range. The wide switching frequency range allows the device to meet a wide range of design requirements. It can be optimized to very small solution size with higher frequency or to very high efficiency with lower switching frequency. It has very small minimum HS MOSFET on-time ( $t_{ON-MIN}$ ) and minimum off-time ( $t_{OFF-MIN}$ ) to provide wide range of voltage conversion. Automated frequency foldback is employed under  $t_{ON-MIN}$  or  $t_{OFF-MIN}$  condition to further extend the operation range.

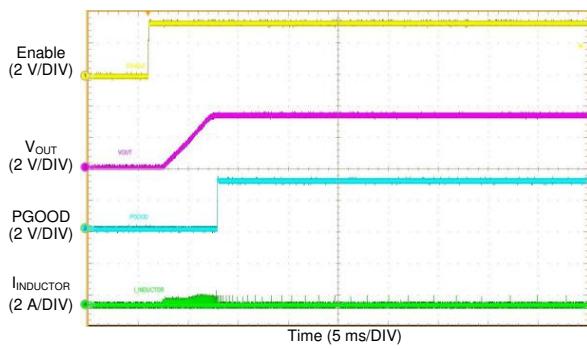

The LM76002-Q1/LM76003-Q1 also features a power-good (PGOOD) flag, precision enable, internal or adjustable soft-start rate, start-up with pre-bias voltage, and output voltage tracking. It provides a both flexible and easy-to-use solution for wide range of applications. Protection features include thermal shutdown, V<sub>CC</sub> undervoltage lockout, cycle-by-cycle current limiting, and short-circuit hiccup protection.

The family requires very few external components and has a pinout designed for simple, optimum PCB layout for EMI and thermal performance. The LM76002-Q1/LM76003-Q1 device is available in a 30-pin WQFN lead-less package.

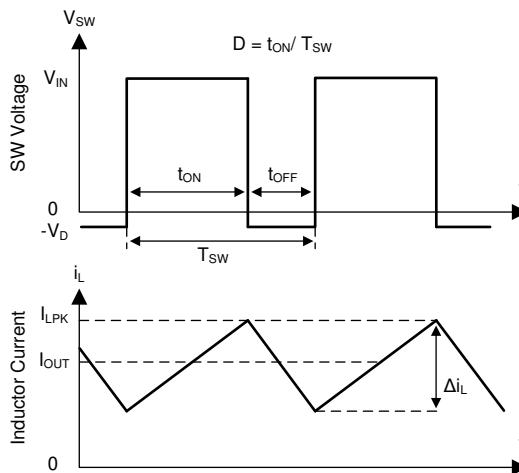

### 7.2 Functional Block Diagram

## 7.3 Feature Description

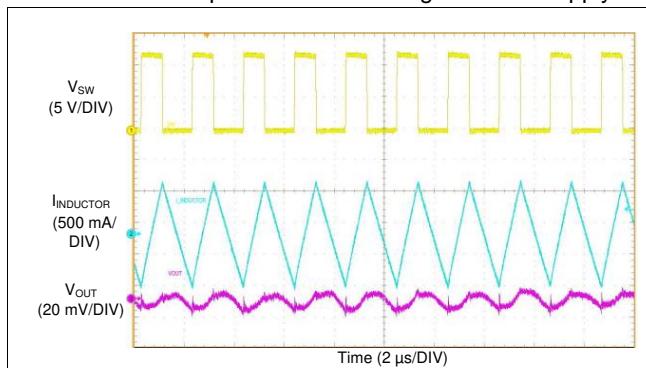

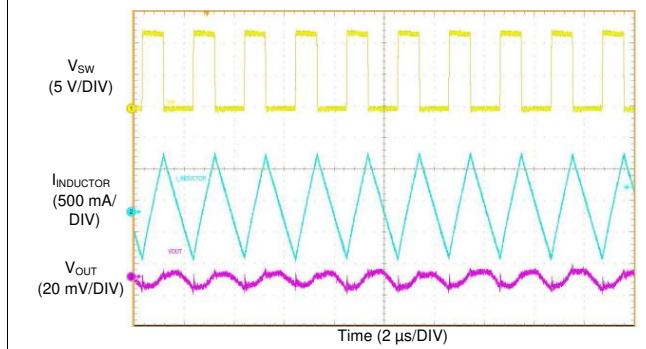

### 7.3.1 Fixed-Frequency, Peak-Current-Mode Control

The following operation description of the LM76002-Q1/LM76003-Q1 refers to the *Functional Block Diagram* and to the waveforms in [Figure 10](#). The LM76002-Q1/LM76003-Q1 supplies a regulated output voltage by turning on the internal high side (HS) and low side (LS) NMOS switches with varying duty cycle (D). During high-side switch on-time  $t_{ON}$ , the SW pin voltage  $V_{SW}$  swings up to approximately  $V_{IN}$ , and the inductor current  $i_L$  increase with linear slope. The HS switch is off by the control logic. During the HS switch off-time,  $t_{OFF}$ , the LS switch is turned on. Inductor current discharges through the LS switch, which forces the  $V_{SW}$  to swing below ground by the voltage drop across the LS switch. The regulator loop adjusts the duty cycle to maintain a constant output voltage. The control parameter of buck converter is defined as duty cycle  $D = t_{ON} / T_{SW}$ . In an ideal buck converter, where losses are ignored, D is proportional to the output voltage and inversely proportional to the input voltage:  $D = V_{OUT} / V_{IN}$ .

**Figure 10. SW Node and Inductor Current Waveforms in Continuous Conduction Mode**

The LM76002-Q1/LM76003-Q1 synchronous buck converter employs peak current-mode control topology. A voltage-feedback loop is used to get accurate DC-voltage regulation by adjusting the peak current command based on voltage offset. The peak inductor current is sensed from the HS switch and compared to the peak current to control the on-time of the HS switch. The voltage feedback loop is internally compensated, which allows command for fewer external components, makes it easy to design, and provides stable operation with almost any combination of output capacitors. The regulator operates with fixed switching frequency in continuous conduction mode (CCM) and discontinuous conduction mode (DCM). At very light load, the LM76002-Q1/LM76003-Q1 operates in PFM to maintain high efficiency, and the switching frequency decreases with reduced load current.

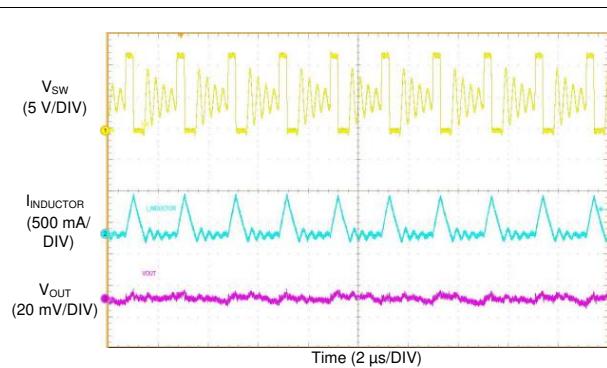

### 7.3.2 Light Load Operation Modes — PFM and FPWM

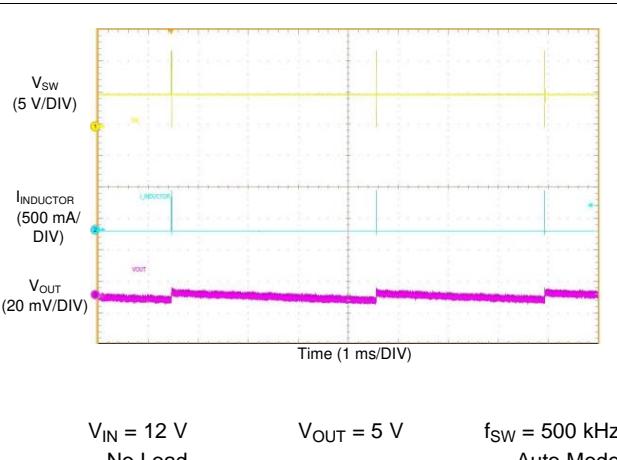

DCM operation is employed in the LM76002-Q1/LM76003-Q1 when the inductor current valley reaches zero. The LM76002-Q1/LM76003-Q1 is in DCM when load current is less than half of the peak-to-peak inductor current ripple in CCM. In DCM, the LS switch is turned off when the inductor current reaches zero. Switching loss is reduced by turning off the LS FET at zero current, and the conduction loss is lowered by not allowing negative current conduction. Power conversion efficiency is higher in DCM than CCM under the same conditions.

In DCM, the HS switch on-time reduces with lower load current. When either the minimum HS switch on-time ( $t_{ON-MIN}$ ) or the minimum peak inductor current ( $I_{PEAK-MIN}$ ) is reached, the switching frequency decreases to maintain regulation. At this point, the LM76002-Q1/LM76003-Q1 operates in PFM. In PFM, switching frequency is decreased by the control loop when load current reduces to maintain output voltage regulation. Switching loss is further reduced in PFM operation due to less frequent switching actions.

## Feature Description (continued)

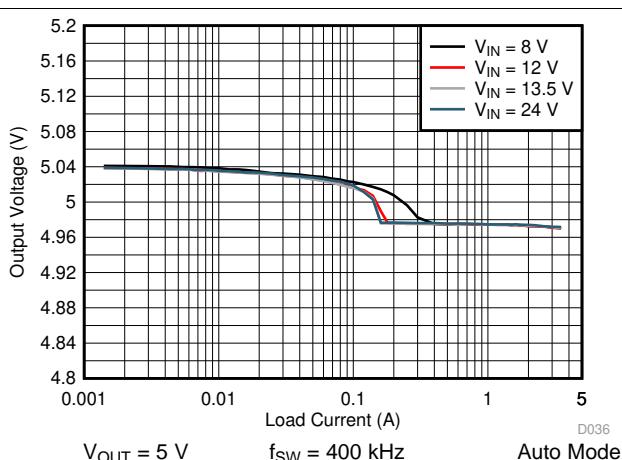

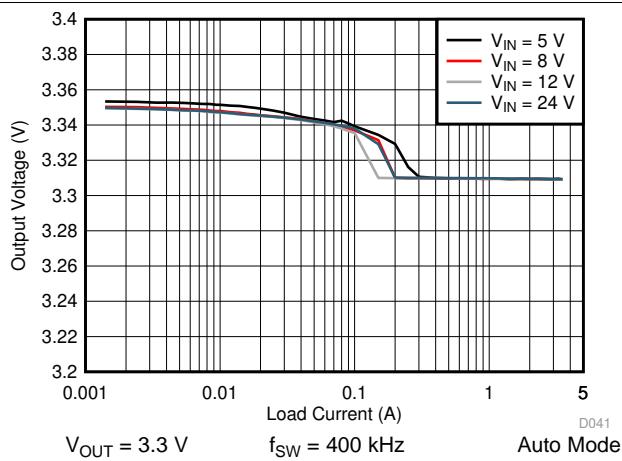

In PFM operation, a small positive DC offset is required at the output voltage to activate the PFM detector. The lower the frequency is in PFM, the more DC offset is needed at  $V_{OUT}$ . See [Typical Characteristics](#) for typical DC offset at very light load. If the DC offset on  $V_{OUT}$  is not acceptable for a given application, TI recommends a static load at output to reduce or eliminate the offset. Lowering values of the feedback divider  $R_{FBT}$  and  $R_{FBB}$  can also serve as a static load. In conditions with low  $V_{IN}$  and/or high frequency, the LM76002-Q1/LM76003-Q1 may not enter PFM mode if the output voltage cannot be charged up to provide the trigger to activate the PFM detector. Once the LM76002-Q1/LM76003-Q1 is operating in PFM mode at higher  $V_{IN}$ , it remains in PFM operation when  $V_{IN}$  is reduced.

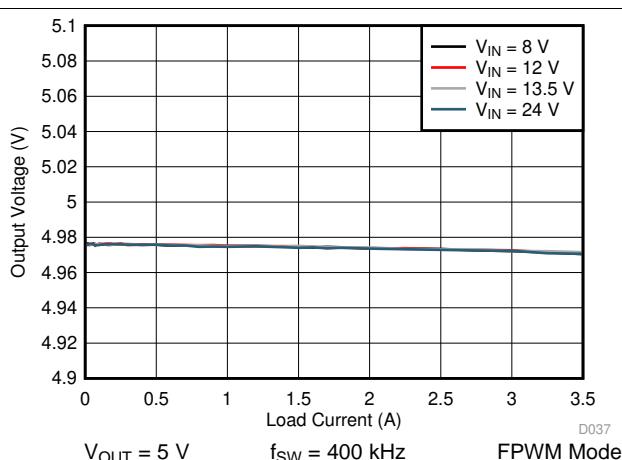

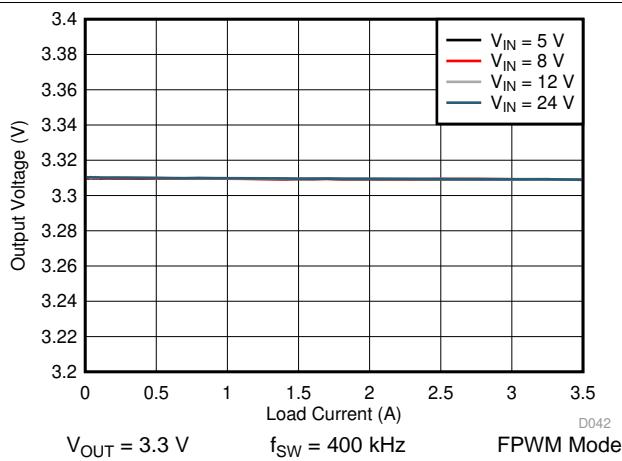

Alternatively, the device can run in a forced pulse-width-modulation (FPWM) mode where the switching frequency does not lower with load, and no offset is added to affect the  $V_{OUT}$  accuracy unless the minimum on-time of the converter is reached.

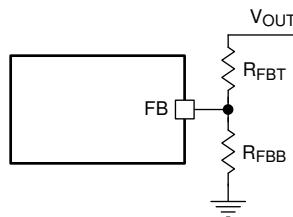

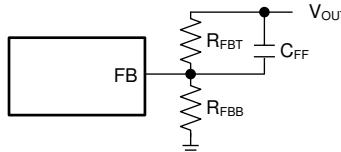

### 7.3.3 Adjustable Output Voltage

The voltage regulation loop in the LM76002-Q1/LM76003-Q1 regulates the FB voltage to be the same as the internal reference voltage. The output voltage of the LM76002-Q1/LM76003-Q1 is set by a resistor divider to program the ratio from  $V_{OUT}$  to  $V_{FB}$ . The resistor divider is connected from the output node to ground with the mid-point connecting to the FB pin.

**Figure 11. Output Voltage Setting**

The voltage reference system produces a precise  $\pm 1\%$  voltage reference over temperature. TI recommends using divider resistors with 1% tolerance or better with temperature coefficient of 100 ppm or lower. Selection of  $R_{FBT}$  equal or lower than 100 k $\Omega$  is also recommended.  $R_{FBB}$  can be calculated by [Equation 1](#):

$$R_{FBB} = \frac{V_{FB}}{V_{OUT} - V_{FB}} R_{FBT} \quad (1)$$

Larger  $R_{FBT}$  and  $R_{FBB}$  values reduce the current that goes through the divider, thus helping to increase light load efficiency. However, larger values also make the feedback path more susceptible to noise. If efficiency at very light load is not critical in a certain application, TI recommends  $R_{FBT} = 10\text{ k}\Omega$  to  $100\text{ k}\Omega$ . If the resistor divider is not connected properly, output voltage cannot be regulated because the feedback loop is broken. If the FB pin is shorted to ground or disconnected, the output voltage is driven close to  $V_{IN}$  because the regulator detects very low voltage on the FB node. The load connected to  $V_{OUT}$  could be damaged in this case. It is important to route the feedback trace away from the noisy area of the PCB. For more layout recommendations, see [Layout](#).

The minimum output voltage achievable equals  $V_{FB}$ , with  $R_{FBB}$  open. The maximum  $V_{OUT}$  is limited by the maximum duty cycle at a given frequency:

$$D_{MAX} = 1 - (t_{OFF\_MIN} / T_{SW})$$

where

- $t_{OFF\_MIN}$  is the minimum off time of the HS switch

- $T_{SW} = 1 / f_{SW}$  is the switching period

(2)

Ideally, without frequency foldback,  $V_{OUT\_MAX} = V_{IN\_MIN} \times D_{MAX}$

Maximum output voltage with frequency foldback can be estimated using [Equation 3](#):

$$V_{OUT\_MAX} = V_{IN\_MIN} \times \frac{t_{ON\_MAX}}{t_{ON\_MAX} + t_{OFF\_MIN}} - I_{OUT} \times (R_{DS\_ON\_HS} + DCR) \quad (3)$$

## Feature Description (continued)

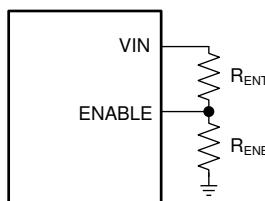

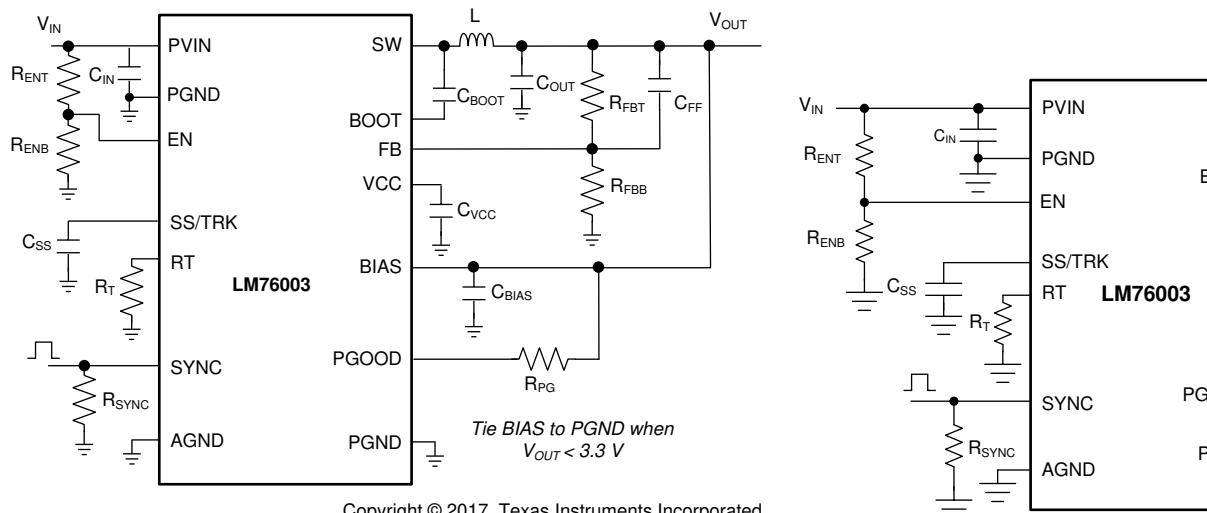

### 7.3.4 Enable (EN Pin) and UVLO

System UVLO by EN and  $V_{CC\_UVLO}$  voltage on the EN pin ( $V_{EN}$ ) controls the ON/OFF functionality of the LM76002-Q1/LM76003-Q1. Applying a voltage less than 0.3 V to the EN input shuts down the operation of the LM76002-Q1/LM76003-Q1. In shutdown mode the quiescent current drops to typically 1.2  $\mu$ A at  $V_{IN} = 24$  V.

The internal LDO output voltage  $V_{CC}$  is turned on when  $V_{EN\_VOUT\_H}$  is higher than 1.15 V. The LM76002-Q1/LM76003-Q1 switching action and output regulation are enabled when  $V_{EN}$  is greater than 1.204 V (typical). The LM76002-Q1/LM76003-Q1 supplies regulated output voltage when enabled and output current up to 2.5 A/3.5 A. The EN pin is an input and cannot be open circuit or floating. The simplest way to enable the operation of the LM76002-Q1/LM76003-Q1 is to connect the EN pin to PVIN pins directly. This allows self-start-up of the LM76002-Q1/LM76003-Q1 when  $V_{IN}$  is within the operation range.

Many applications may benefit from the employment of an enable divider  $R_{ENT}$  and  $R_{ENB}$  (see [Figure 12](#)) to establish a precision system UVLO level for the stage. System UVLO can be used for supplies operating from utility power as well as battery power. It can be used for sequencing, ensuring reliable operation, or supply protection, such as a battery. An external logic signal can also be used to drive EN input for system sequencing and protection.

**Figure 12.  $V_{IN}$  UVLO**

With a selected  $R_{ENT}$ , the  $R_{ENB}$  can be calculated by:

$$R_{ENB} = \frac{V_{EN\_VOUT\_H} \times R_{ENT}}{V_{IN\_ON\_H} - V_{EN\_VOUT\_H}}$$

where

- $V_{IN\_ON\_H}$  is the desired supply voltage threshold to turn on this device

- $V_{EN\_VOUT\_H}$  could be taken from device data sheet

(4)

Note that the divider adds to supply quiescent current by  $V_{IN} / (R_{ENT} + R_{ENB})$ . Small  $R_{ENT}$  and  $R_{ENB}$  values add more quiescent current loss. However, large divider values make the node more sensitive to noise.  $R_{ENT}$  in the hundreds of k $\Omega$  range is a good starting point.

### 7.3.5 Internal LDO, VCC UVLO, and Bias Input

The LM76002-Q1/LM76003-Q1 has an internal LDO generating VCC voltage for control circuitry and MOSFET drivers. The nominal voltage for VCC is 3.29 V. The VCC pin must have a 1- $\mu$ F to 4.7- $\mu$ F bypass capacitor placed as close as possible to the pin and properly grounded. Do not load or short the VCC pin to ground during operation. Shorting the VCC pin to ground during operation may damage the device.

An UVLO prevents the LM76002-Q1/LM76003-Q1 from operating until the VCC voltage exceeds  $V_{CC\_UVLO}$ . The  $V_{CC\_UVLO}$  threshold is 3.14 V and has approximately 575 mV of hysteresis, so the device operates until VCC drops below 2.575 V (typical). Hysteresis prevents the device from turning off during power up if  $V_{IN}$  drops due to input current demands.

## Feature Description (continued)

The LDO can generate  $V_{CC}$  from two inputs: the supply voltage  $V_{IN}$  and the BIAS input. The LDO power loss is calculated by  $I_{LDO} \times (V_{INLDO} - V_{OUTLDO})$ . The higher the difference between the input and output voltages of the LDO, the more losses occur to supply the same LDO output current. The BIAS input is designed to reduce the difference of the input and output voltages of the LDO to improve efficiency, especially at light load. TI recommends tying the BIAS pin to  $V_{OUT}$  when the output voltage is equal to or greater than 3.3 V. Tie the BIAS pin to ground for applications less than 3.3 V. BIAS can also tie to external voltage source if available to improve efficiency. When used, TI recommends a 1- $\mu$ F to 10- $\mu$ F high-quality ceramic capacitor be used to bypass the BIAS pin to ground. If there is high-frequency noise or voltage spikes present on  $V_{OUT}$  (during transient events or fault conditions), TI recommends connecting a resistor (1 to 10  $\Omega$ ) between  $V_{OUT}$  and BIAS.

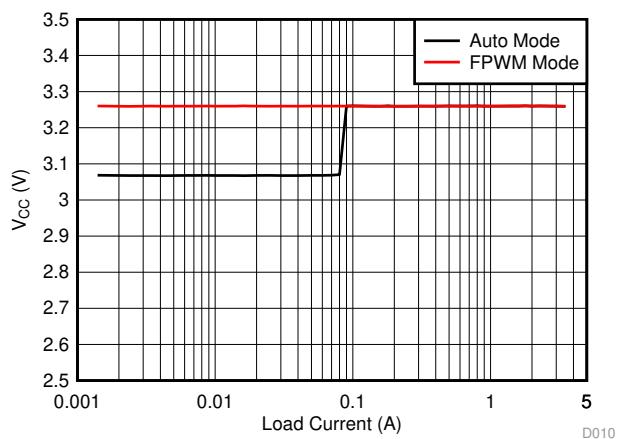

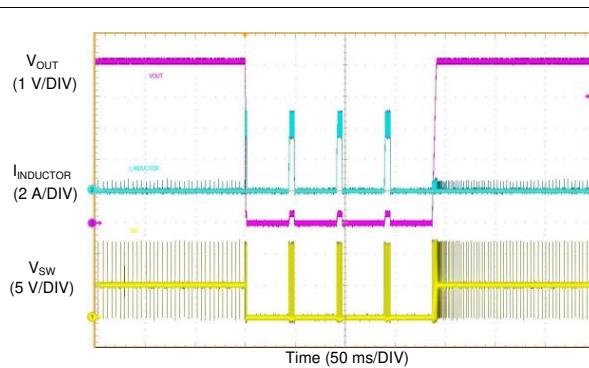

The  $V_{CC}$  voltage is typically 3.27 V. When the LM76002-Q1/LM76003-Q1 is operating in PFM mode with frequency foldback,  $V_{CC}$  voltage is reduced to 3.1 V (typical) to further decrease the quiescent current and improve efficiency at very light loads. [Figure 13](#) shows an example of  $V_{CC}$  voltage change with mode change.

**Figure 13.  $V_{CC}$  Voltage Change With Mode Change**

$V_{CC}$  voltage has an internal undervoltage lockout threshold,  $V_{CC\_UVLO}$ . When  $V_{CC}$  voltage is higher than  $V_{CC\_UVLO}$  rising threshold, the device is active and in normal operation if  $V_{EN} > V_{EN\_VOUT\_H}$ . If  $V_{CC}$  voltage drops below  $V_{CC\_UVLO}$  falling threshold, the  $V_{OUT}$  is shut down.

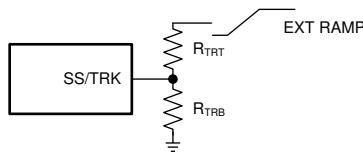

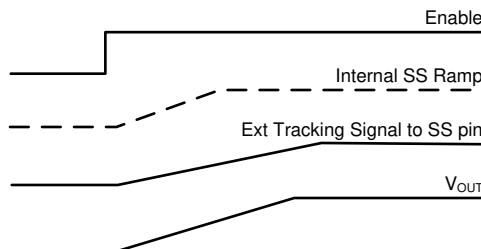

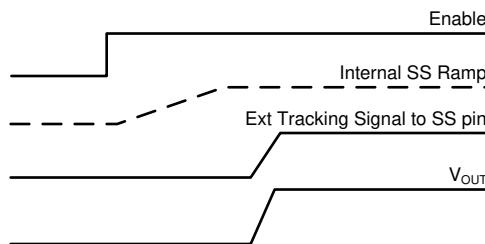

### 7.3.6 Soft Start and Voltage Tracking (SS/TRK)

The LM76002-Q1/LM76003-Q1 has a flexible and easy-to-use start-up rate control pin: SS/TRK. The soft-start feature is to prevent inrush current impacting the LM76002-Q1/LM76003-Q1, and its supply when power is first applied. Soft start is achieved by slowly ramping up the target regulation voltage when the device is first enabled or powered up. The simplest way to use the device is to leave the SS/TRK pin open circuit or floating. The LM76002-Q1/LM76003-Q1 employs the internal soft-start control ramp and starts up to the regulated output voltage in 6.3 ms typically. In applications with a large amount of output capacitors, higher  $V_{OUT}$ , or other special requirements, the soft-start time can be extended by connecting an external capacitor  $C_{SS}$  from SS/TRK pin to AGND. Extended soft-start time further reduces the supply current required to charge up output capacitors and supply any output loading. An internal current source ( $I_{SSC} = 2.2 \mu A$ ) charges  $C_{SS}$  and generates a ramp from 0 V to  $V_{FB}$  to control the ramp-up rate of the output voltage. For a desired soft-start time  $t_{SS}$ , the capacitance for  $C_{SS}$  can be found by [Equation 5](#):

## Feature Description (continued)

$$C_{SS} = I_{SSC} \times t_{SS}$$

where

- $C_{SS}$  = soft-start capacitor value ( $\mu F$ )

- $I_{SSC}$  = soft-start charging current ( $\mu A$ )

- $t_{SS}$  = desired soft-start time (s)

(5)

The soft-start capacitor  $C_{SS}$  is discharged by an internal FET when  $V_{OUT}$  is shut down by hiccup protection or  $ENABLE$  = logic low. When a large  $C_{SS}$  is applied, and  $EN$  is toggled low only for a short period of time,  $C_{SS}$  may not be fully discharged. The next soft-start ramp follows internal soft-start ramp before reaching the leftover voltage on  $C_{SS}$  and then follows the ramp programmed by  $C_{SS}$ . If this is not acceptable for a certain application, an R-C low-pass filter can be added to  $EN$  to slow down the shutting down of  $VCC$ , allowing more time to discharge  $C_{SS}$ .

The LM76002-Q1/LM76003-Q1 is capable of start-up into pre-biased output conditions. When the inductor current reaches zero, the LS switch is turned off to avoid negative current conduction. This operation mode is also called diode emulation mode. It is built in by the DCM operation in light loads. With a pre-biased output voltage, the LM76002-Q1/LM76003-Q1 waits until the soft-start ramp allows regulation above the pre-biased voltage and then follows the soft-start ramp to the regulation level. When an external voltage ramp is applied to the SS/TRK pin, the LM76002-Q1/LM76003-Q1 FB voltage follows the ramp if the ramp magnitude is lower than the internal soft-start ramp. A resistor divider pair can be used on the external control ramp to the SS/TRK pin to program the tracking rate of the output voltage. The final voltage detected by the SS/TRK pin must not fall below 1.2 V to avoid abnormal operation.

$V_{OUT}$  tracked to an external voltage ramp has the option of ramping up slower or faster than the internal voltage ramp.  $V_{FB}$  always follows the lower potential of the internal voltage ramp and the voltage on the SS/TRK pin. [Figure 14](#) shows resistive divider connection if external ramp tracking is desired.

**Figure 14. Soft-Start Tracking External Ramp**

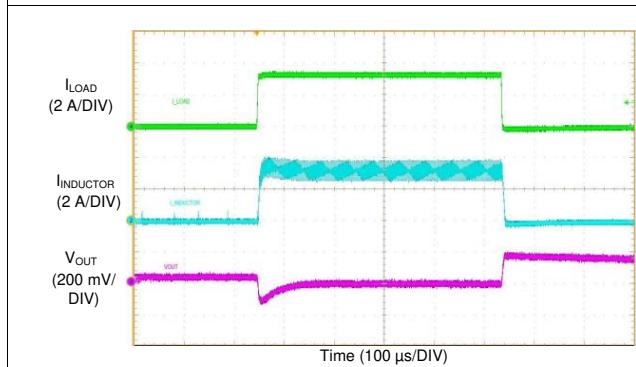

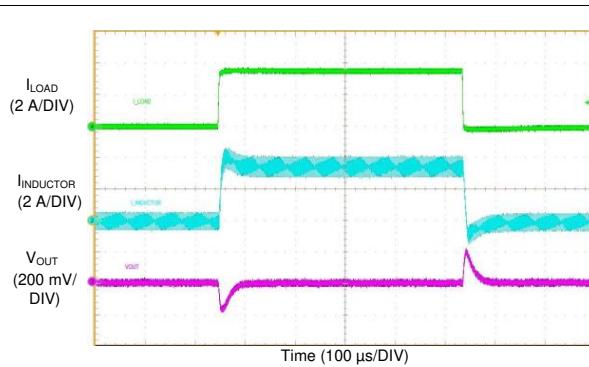

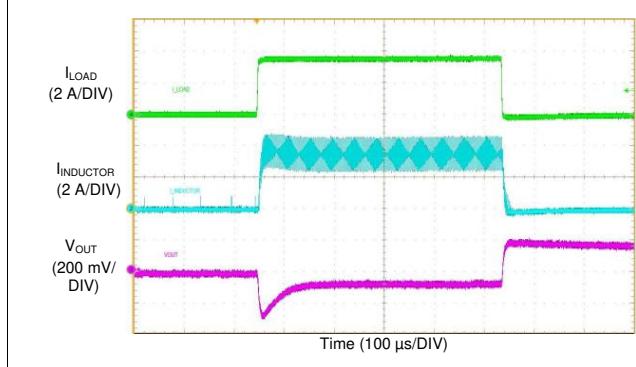

[Figure 15](#) shows the case when  $V_{OUT}$  ramps more slowly than the internal ramp, while [Figure 16](#) shows when  $V_{OUT}$  ramps faster than the internal ramp. Faster start-up time may result in inductor current tripping current protection during start-up. Use with special care.

**Figure 15. Tracking With Longer Start-up Time Than The Internal Ramp**

## Feature Description (continued)

**Figure 16. Tracking With Shorter Start-up Time Than The Internal Ramp**

The LM76002-Q1/LM76003-Q1 is capable of start-up into pre-biased output conditions. During start-up the device sets the minimum inductor current to zero to avoid discharging a pre-biased load.

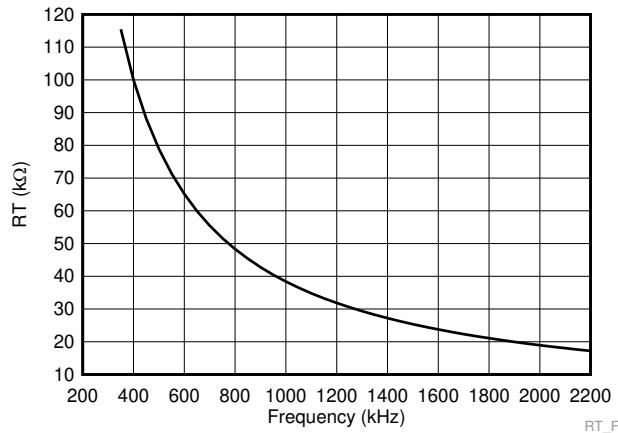

### 7.3.7 Adjustable Switching Frequency (RT) and Frequency Synchronization

The switching frequency of the LM76002-Q1/LM76003-Q1 can be programmed by the impedance  $R_T$  from the RT pin to ground. The frequency is inversely proportional to the  $R_T$  resistance. The RT pin can be left floating, and the LM76002-Q1/LM76003-Q1 operates at 500-kHz default switching frequency. The RT pin is not designed to be shorted to ground.

For an desired frequency,  $R_T$  can be found by:

$$R_T(\text{k}\Omega) = \frac{38400}{\text{Frequency(kHz)} - 14.33} \quad (6)$$

**Figure 17. Switching Frequency vs RT**

**Table 1. Switching Frequency vs RT**

| SWITCHING FREQUENCY (kHz) | RT RESISTANCE (kΩ) |

|---------------------------|--------------------|

| 300                       | 134.42             |

| 400                       | 99.57              |

| 500                       | 79.07              |

| 750                       | 52.20              |

| 1000                      | 38.96              |

| 1500                      | 25.85              |

| 2000                      | 19.34              |

| 2200                      | 17.57              |

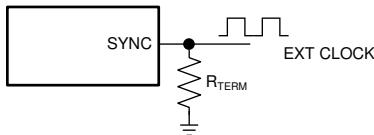

The LM76002-Q1/LM76003-Q1 switching action can also be synchronized to an external clock from 300 kHz to 2.2 MHz. TI recommends connecting an external clock to the SYNC pin with appropriate termination resistor. Ground the SYNC pin if not used.

**Figure 18. Frequency Synchronization**

The recommendations for the external clock include high level no lower than 2 V, low level no higher than 0.4 V, duty cycle between 10% and 90%, and both positive and negative pulse width no shorter than 80 ns. When the external clock fails at logic high or low, the LM76002-Q1/LM76003-Q1 switches at the frequency programmed by the  $R_T$  resistor after a time-out period. TI recommends connecting a resistor  $R_T$  to the RT pin so that the internal oscillator frequency is the same as the target clock frequency when the LM76002-Q1/LM76003-Q1 is synchronized to an external clock. This allows the regulator to continue operating at approximately the same switching frequency if the external clock fails.

The choice of switching frequency is usually a compromise between conversion efficiency and the size of the circuit. Lower switching frequency implies reduced switching losses (including gate charge losses, switch transition losses, etc.) and usually results in higher overall efficiency. However, higher switching frequency allows use of smaller LC output filters and hence a more compact design. Lower inductance also helps transient response (higher large signal slew rate of inductor current), and reduces the DCR loss. The optimal switching frequency is usually a trade-off in a given application and thus needs to be determined on a case-by-case basis. It is related to the input voltage, output voltage, most frequent load current level(s), external component choices, and circuit size requirement. The choice of switching frequency may also be limited if an operating condition triggers  $t_{ON-MIN}$  or  $t_{OFF-MIN}$ .

### 7.3.8 Minimum On-Time, Minimum Off-Time, and Frequency Foldback at Dropout Conditions

Minimum on-time,  $t_{ON-MIN}$ , is the smallest duration of time that the HS switch can be on.  $t_{ON-MIN}$  is typically 65 ns in the LM76002-Q1/LM76003-Q1. Minimum off-time,  $t_{OFF-MIN}$ , is the smallest duration that the HS switch can be off.  $t_{OFF-MIN}$  is typically 95 ns in the LM76002-Q1/LM76003-Q1. In CCM operation,  $t_{ON-MIN}$  and  $t_{OFF-MIN}$  limits the voltage conversion range given a selected switching frequency. The minimum duty cycle allowed is:

$$D_{MIN} = t_{ON-MIN} \times f_{SW} \quad (7)$$

And the maximum duty cycle allowed is:

$$D_{MAX} = 1 - t_{OFF-MIN} \times f_{SW} \quad (8)$$

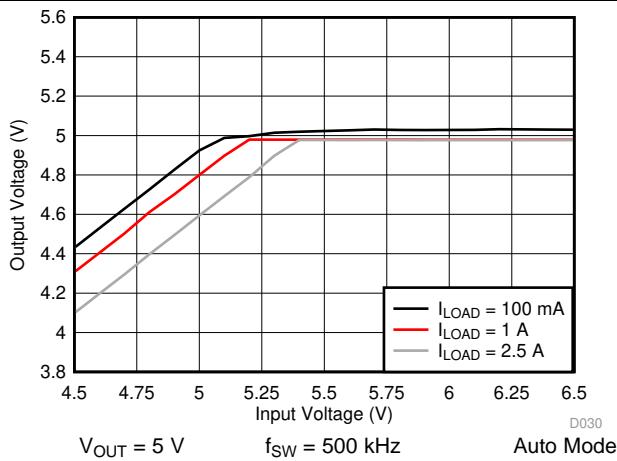

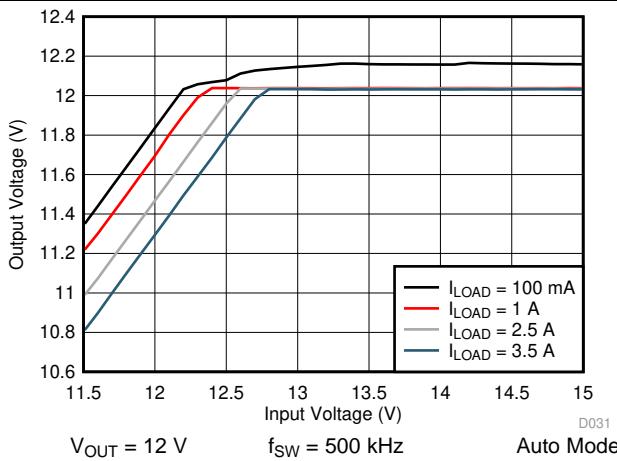

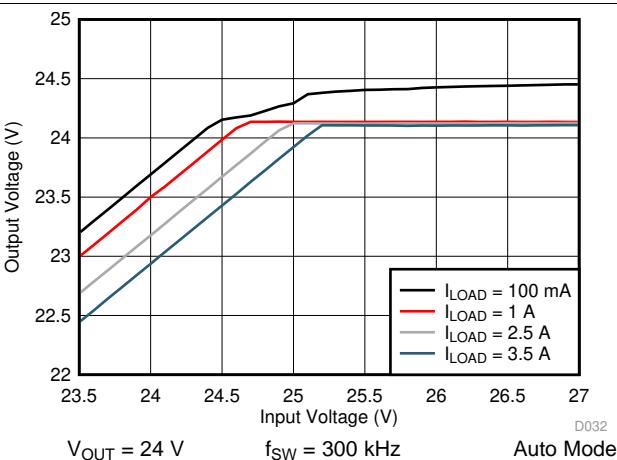

Given fixed  $t_{ON-MIN}$  and  $t_{OFF-MIN}$ , the higher the switching frequency the narrower the range of the allowed duty cycle. In the LM76002-Q1/LM76003-Q1, frequency foldback scheme is employed to extend the maximum duty cycle when  $t_{OFF-MIN}$  is reached. The switching frequency decreases once longer duty cycle is needed under low  $V_{IN}$  conditions. The switching frequency can be decreased to approximately 1/10 of the programmed frequency by RT or the synchronization clock. Such a wide range of frequency foldback allows the LM76002-Q1/LM76003-Q1 output voltage to stay in regulation with a much lower supply voltage  $V_{IN}$ . This leads to a lower effective dropout voltage. See [Typical Characteristics](#) for more details.

Given an output voltage, the choice of the switching frequency affects the allowed input voltage range, solution size and efficiency. The maximum operational supply voltage can be found by:

$$V_{IN\_MAX} = V_{OUT} / (f_{SW} \times t_{ON-MIN}) \quad (9)$$

At lower supply voltage, the switching frequency decreases once  $t_{OFF-MIN}$  is tripped. The minimum  $V_{IN}$  without frequency foldback can be approximated by:

$$V_{IN\_MIN} = V_{OUT} / (f_{SW} \times t_{OFF-MIN}) \quad (10)$$

Considering power losses in the system with heavy load operation,  $V_{IN-MIN}$  is higher than the result calculated in [Equation 10](#). With frequency foldback,  $V_{IN-MIN}$  is lowered by decreased  $f_{SW}$ . When the device is operating in auto mode at voltages near maximum rated input voltage and light load conditions, an increased output voltage ripple during load transient may be observed. For this reason TI recommends that device operating point be calculated with sufficient operational margin so that minimum on-time condition is not triggered.

### 7.3.9 Internal Compensation and $C_{FF}$

The LM76002-Q1/LM76003-Q1 is internally compensated with  $R_C = 600\text{ k}\Omega$  and  $C_C = 35\text{ pF}$  as shown in the [Functional Block Diagram](#). The internal compensation is designed such that the loop response is stable over the entire operating frequency and output voltage range. Depending on the output voltage, the compensation loop phase margin can be low with all ceramic capacitors. TI recommends placing an external feed-forward cap  $C_{FF}$  in parallel with the top resistor divider  $R_{FBT}$  for optimum transient performance.

Figure 19. Feed-Forward Capacitor for Loop Compensation

The feed-forward capacitor  $C_{FF}$  in parallel with  $R_{FBT}$  places an additional zero before the crossover frequency of the control loop to boost phase margin. The zero frequency can be found by [Equation 11](#):

$$f_{Z-CFF} = 1 / (2\pi \times R_{FBT} \times C_{FF}) \quad (11)$$

An additional pole is also introduced with  $C_{FF}$  at the frequency of [Equation 12](#):

$$f_{P-CFF} = 1 / (2\pi \times C_{FF} \times (R_{FBT} // R_{FBB})) \quad (12)$$

Select the  $C_{FF}$  so that the bandwidth of the control loop without the  $C_{FF}$  is centered between  $f_{Z-CFF}$  and  $f_{P-CFF}$ . The zero  $f_{Z-CFF}$  adds phase boost at the crossover frequency and improves transient response. The pole  $f_{P-CFF}$  helps maintaining proper gain margin at frequency beyond the crossover.

Electrolytic capacitors have much larger ESR and the ESR zero frequency would be low enough to boost the phase up around the crossover frequency.

$$f_{Z-ESR} = 1 / (2\pi \times ESR \times C_{OUT}) \quad (13)$$

Designs using mostly electrolytic capacitors at the output may not need any  $C_{FF}$ . The  $C_{FF}$  creates a time constant with  $R_{FBT}$  that couples in the attenuated output voltage ripple to the FB node. If the  $C_{FF}$  value is too large, it can couple too much ripple to the FB and affect  $V_{OUT}$  regulation. It could also couple too much transient voltage deviation and falsely trip PGOOD thresholds. Therefore, calculate  $C_{FF}$  based on output capacitors used in the system. At cold temperatures, the value of  $C_{FF}$  might change based on the tolerance of the chosen component. This may reduce its impedance and ease noise coupling on the FB node. To avoid this, more capacitance can be added to the output or the value of  $C_{FF}$  can be reduced. See [Feed-Forward Capacitor](#) for the calculation of  $C_{FF}$ .

### 7.3.10 Bootstrap Voltage and VBOOT UVLO (BOOT Pin)

The driver of the power switch (HS switch) requires bias higher than  $V_{IN}$  when the HS switch is ON. The capacitor connected between  $C_{BOOT}$  and SW works as a charge pump to boost voltage on the BOOT pin to ( $V_{SW} + V_{CC}$ ). The boot diode is integrated on the LM76002-Q1/LM76003-Q1 die to minimize physical size. TI recommends a 0.47- $\mu\text{F}$ , 6.3-V or higher capacitor for  $C_{BOOT}$ . The  $V_{BOOT\_UVLO}$  threshold is typically 2.2 V. If the  $C_{BOOT}$  capacitor is not charged above this voltage with respect to SW, the device initiates a charging sequence using the low-side FET.

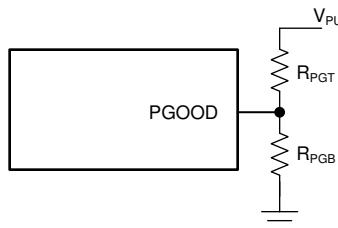

### 7.3.11 Power Good and Overvoltage Protection (PGOOD)

The LM76002-Q1/LM76003-Q1 has a built-in power-good flag shown on PGOOD pin to indicate whether the output voltage is within its regulation level. The PGOOD signal can be used for start-up sequencing of multiple rails. The PGOOD pin is an open-drain output that requires a pullup resistor to an appropriate logic voltage (any voltage below 12 V). The pin can sink 5 mA of current and maintain its specified logic low level. A typical range of pullup resistor value is 10 k $\Omega$  to 100 k $\Omega$ . When the FB voltage is outside the power-good band, +10% above and -10% below the internal reference  $V_{REF}$  typically, the PGOOD switch is turned on, and the PGOOD pin voltage is pulled to ground. When the FB is 2% (typical) closer to FB than the PGOOD threshold, the PGOOD switch is turned off, and the pin is pulled up to the voltage connected to the pullup resistor. Both rising and falling edges of the power-good flag have a built-in 220- $\mu\text{s}$  (typical) deglitch delay. To pull up PGOOD pin to a voltage higher than 15V, a resistor divider can be used to divide the voltage down.

**Figure 20. PGOOD Resistor Divider**

For given pullup voltage  $V_{PU}$  and desired voltage on PGOOD pin is  $V_{PG}$  and with  $R_{PGT}$  chosen, value for  $R_{PGB}$  can be calculated using [Equation 14](#):

$$R_{PGB} = \frac{V_{PG}}{V_{PU} - V_{PG}} R_{PGT} \quad (14)$$

### 7.3.12 Overcurrent and Short-Circuit Protection

The LM76002-Q1/LM76003-Q1 is protected from overcurrent conditions by cycle-by-cycle current limiting on both peak and valley of the inductor current. Hiccup mode is activated if a fault condition persists to prevent overheating.

High-side MOSFET overcurrent protection is implemented by the nature of the peak current-mode control. The HS switch current is sensed when the HS is turned on after a blanking time. The HS switch current is compared to the either the minimum of a fixed current set point ( $I_{SC}$ ) or the output of the voltage regulation loop minus slope compensation every switching cycle. The slope compensation increases with duty cycle and tends to lower the HS current limit above 60% duty cycle as it lowers below  $I_{SC}$ . See [Typical Characteristics](#).

When the LS switch is turned on, the current going through it is also sensed and monitored. Before turning off the LS switch at the end of every clock cycle, the LS current is compared to the LS current limit. If the LS current limit is exceeded, the LS MOSFET stays on, and the HS switch is not turned on. The LS switch is kept ON so that inductor current keeps ramping down, until the inductor current ramps below  $I_{LSLIMIT}$ . The LS switch is turned off once the LS current falls below the limit, and the HS switch is turned on again after a dead time.

If the current of the LS switch is higher than the LS current limit for 128 consecutive cycles, and the feedback voltage falls 60% below regulation, hiccup current-protection mode is activated. In hiccup mode, the regulator is shut down and kept off for 46 ms typically before the LM76002-Q1/LM76003-Q1 tries to start again. If overcurrent or a short-circuit fault condition still exists, hiccup repeats until the fault condition is removed. Hiccup mode reduces power dissipation under severe overcurrent conditions, and prevents overheating and potential damage to the device. Under non-severe overcurrent conditions when the feedback voltage has not fallen 60% below regulation, the LM76002-Q1/LM76003-Q1 reduces the switching frequency and keeps the inductor current valley clamped at the LS current limit level. This operation mode allows slight overcurrent operation during load transients without tripping hiccup.

If tracking was used for initial sequencing the device attempts to restart using the internal soft-start circuit until the tracking voltage is reached.

### 7.3.13 Thermal Shutdown

Thermal shutdown limits total power dissipation by turning off the internal switches when the device junction temperature exceeds 160°C (typical). After thermal shutdown occurs, hysteresis prevents the device from switching until the junction temperature drops to approximately 135°C. When the junction temperature falls below 135°C, the LM76002-Q1/LM76003-Q1 attempts to soft start.

## 7.4 Device Functional Modes

### 7.4.1 Shutdown Mode

The EN pin provides electrical on/off control for the LM76002-Q1/LM76003-Q1. When the EN pin voltage is below 0.3 V (typical), both the regulator and the internal LDO have no output voltages, and the device is in shutdown mode. In shutdown mode the quiescent current drops to typically 1.2  $\mu$ A. The LM76002-Q1/LM76003-Q1 also employs UVLO protection. If  $V_{CC}$  voltage is below the UVLO level, the output of the regulator is turned off.

### 7.4.2 Standby Mode

The internal LDO has a lower EN threshold than the regulator. When the EN pin voltage is above below 1.1 V (maximum) and below the precision enable threshold for the output voltage, the internal LDO regulates the  $V_{CC}$  voltage at 3.29 V typically. The precision enable circuitry is ON once  $V_{CC}$  is above the UVLO. The internal MOSFETs remain in tri-state unless the voltage on EN pin goes above the precision enable threshold. The LM76002-Q1/LM76003-Q1 also employs UVLO protection. If  $V_{CC}$  voltage is below the UVLO level, the output of the regulator is turned off.

### 7.4.3 Active Mode

The LM76002-Q1/LM76003-Q1 is in active mode when the EN pin and UVLO high threshold levels are satisfied. The simplest way to enable the operation of the LM76002-Q1/LM76003-Q1 is to connect the EN pin to VIN, which allows self start-up of the LM76002-Q1/LM76003-Q1 when the input voltage is in the operation range: 3.5 V to 60 V. See [Enable \(EN Pin\) and UVLO](#) for details on setting these operating levels.

In active mode, depending on the load current, the LM76002-Q1/LM76003-Q1 will be in one of five sub modes:

1. CCM with fixed switching frequency with load between half of  $I_{MINPK}$  to full load.

2. DCM when the load current is lower than half of the inductor current ripple.

3. Light load mode where the device uses pulse frequency modulation (PFM) and lowers the switching frequency at load under half of  $I_{MINPK}$  to improve efficiency.

4. Foldback mode when switching frequency is reduced to maintain output regulation with supply voltages that cause the minimum  $t_{ON}$  or  $t_{OFF}$  to be exceeded.

5. Forced-pulse-width modulation (FPWM) is similar to CCM with fixed switching frequency, but extends the fixed frequency range of operation from full to no load.

### 7.4.4 CCM Mode